COM81C17LJP Ver la hoja de datos (PDF) - SMSC -> Microchip

Número de pieza

componentes Descripción

Lista de partido

COM81C17LJP Datasheet PDF : 18 Pages

| |||

BIT

DESCRIPTION

7 RX BUFFER FULL - This signals the processor that a completed character is present in

the Receive Buffer Register for transfer to the processor. This bit is set when a character

has been loaded from the receive deserialization logic to the Receive Buffer Register.

This bit is cleared by:

A)

Reading the Receive Buffer Register

B)

Asserting the RECEIVER RESET bit in the Control Register

C)

Asserting internal reset

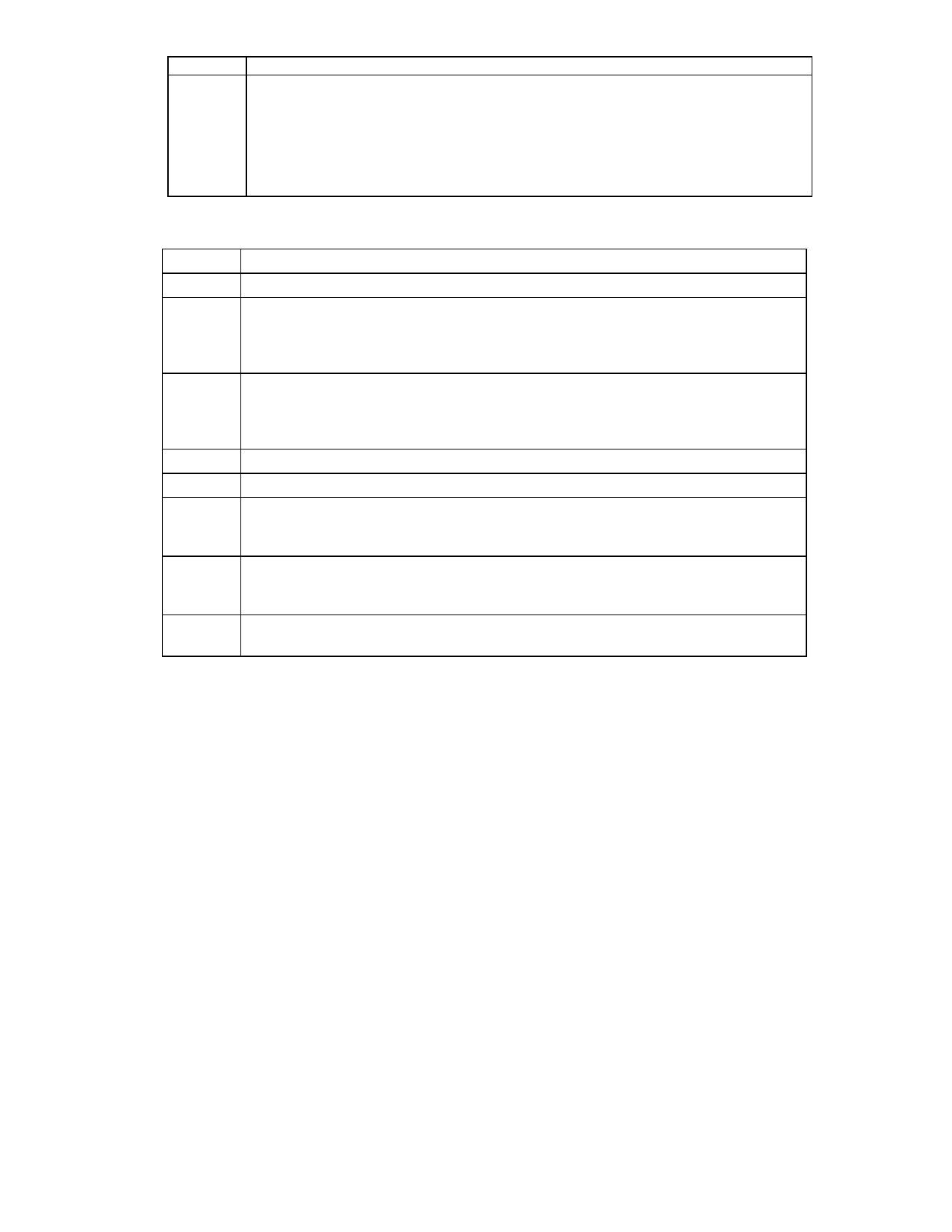

Table 5 – COM81C17 CONTROL REGISTER DESCRIPTION (BITS 0-7)

BIT

DESCRIPTION

0

Not used (test mode bit, must be zero).

1

CP2 – This bit controls the nCP2 output pin. Data at the output is the logical

compliment of the register data. When the CP2 bit is set, the nCP2 pin is forced low.

When CP2 is RTS, a 1 to 0 transition of the CP2 bit will cause the nCP2 pin to go high

one TXc time after the last serial bit has been transmitted.

2

RX ENABLE – This bit when reset will disable the setting of the RX BUFFER FULL bit

in the Status Register which informs the processor of the availability of a received

character in the Receive Buffer Register. The error bits in the Status Register will be

cleared and will remain cleared when RX is disabled.

3

RX RESET – This will reset the receiver block only.

4

TX RESET – This will reset the transmitter block only.

5

TX ENABLE – Data transmission cannot take place by the TPUART unless this bit is

set. When this bit is reset (disable), transmission will be disabled only after the

previously written data has been transmitted.

6

RESET ERRORS – This bit when set will reset the parity, overrun, and framing error

bits in the Status Register. No latch is provided in the Control Register for saving this

bit; therefore there is no need to clear it (error reset = d6.RS.nWR).

7

INTERNAL RESET – This bit enables the resetting of the internal circuitry and initializes

access to address 0 to be sequential.

10