MT8920B-1 Ver la hoja de datos (PDF) - Mitel Networks

Número de pieza

componentes Descripción

Lista de partido

MT8920B-1 Datasheet PDF : 29 Pages

| |||

MT8920B CMOS

Timing information for data transfers on this interface

is shown in Figure 14. The Mode 1 interface is

designed to operate directly with a 68000-type

asynchronous bus but can easily accommodate most

other popular microprocessors as well.

Control Registers

Two control registers allow control of Mode 1

features. Control Register 1 provides bits to select

the type of interrupt, to enable interrupts from two

different and independent sources and to reset the

interrupt registers. Also contained in Control

Register 1 are bits to configure the device for 24 or

32 channel operation and to expand the address

range for convenient access to the second transmit

RAM Tx1. A description of the bit functions in

Control Register 1 is shown in Table 3.

Mode 1 provides various loopback paths and output

configuration options which are controlled by bits in

Control Register 2. Bits D0, D1 of Control Register 2

configure loopbacks using input and output streams

STi0, STo0 as described in Table 4. The input

stream STi0 can be looped back to source the output

stream STo0 as well as receive RAM Rx0. The

transmit RAM Tx0 can be looped to source the

receive RAM Rx0, as well as STo0 and, the transmit

RAM Tx0 can be looped to the receive RAM Rx0

while STi0 sources STo0. The function of these

loopback configurations is shown in Figure 5.

In a similar way, the output STo1 can be reconfigured

for different functionality. Bits D2 and D3 of Control

Register 2 allow STo1 to be sourced, with a one

frame delay via Tx1 from receive stream STi0. STo1

can also output the result of a comparison of the

contents of Tx1 ram with input stream STi0. These

output configurations of STo1 are shown in Figure 6

a and b. Figure 6 c shows the effect of combining

these two features.

Interrupt Registers

Interrupts can be generated in Mode 1 only. Two

channels of the ST-BUS input stream, STi0, can be

selected to provide an interrupt to the system.

Interrupts can be of two types: Static or Dynamic.

Static interrupts are caused when data within a

selected channel matches a given pattern. Dynamic

interrupts occur when bits in a selected channel

change state (1 to 0, 0 to 1 or toggle). Interrupts are

controlled through two identical paths (1 and 2)

consisting of the following registers:

Interrupt Channel Address (1/2): The address

(0-31) of the channel which will generate the

interrupt is stored in this register.

Image Register (1/2): The contents of the

channel causing the interrupt is stored in this

register. Reading this register will clear its contents.

Match Byte Register (1/2): In static mode this

register is used to store the byte which will be

compared with the contents of the selected channel

causing the interrupt.

In dynamic mode, the bits in this register and the

corresponding bit in the Interrupt Mask Register

define the type of dynamic interrupt (i.e., 0 to 1, 1 to

0, toggle). (Refer to Table 5.)

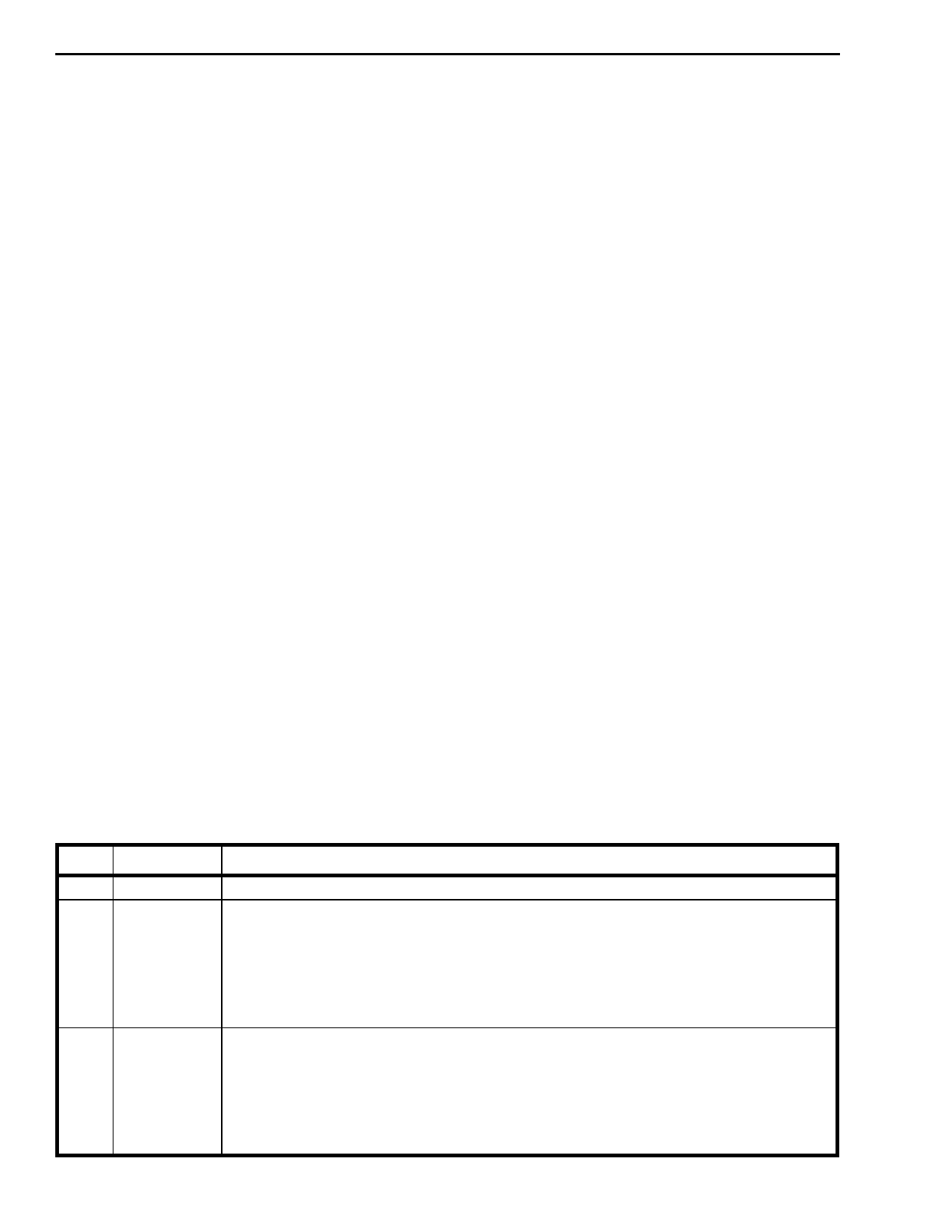

Bit

Name

Description

7-4 (Unused)

3-2

CONFIG STo1 Output Configuration Bits:

D3D2 = 00-

01-

Normal operation. ST-BUS stream from Tx1 is output on STo1 pin.

STi0 stream is output on STo1 pin delayed one frame (Figure 6 a).

10- STi0 is compared through XOR (exclusive OR) with ST-BUS stream

from Tx1 and output at STo1 (Figure 6 b).

11- STi0 stream, delayed one frame (via Tx1), is compared (XOR) with the

next frame arriving at STi0 and the result output at STo1 (Figure 6 c).

1-0 LOOPBACK Internal Loopback Configuration Bits:

D1D0 = 00-

01-

Normal operation. No internal loops.

Loop STi0 to STo0 while still receiving STi0 in Rx0 (Figure 5 a).

10- Loop Tx0 output ST-BUS stream to Rx0 input ST-BUS stream while

outputting Tx0 output to STo0. STi0 is not received (Figure 5 b).

11- Loop Tx0 output ST-BUS stream to Rx0 input ST-BUS stream. Loop

STi0 to STo0 (Figure 5 c).

Table 4. Control Register 2 Bit Definitions

3-10