RTL8100 Ver la hoja de datos (PDF) - Unspecified

Número de pieza

componentes Descripción

Lista de partido

RTL8100 Datasheet PDF : 58 Pages

| |||

RTL8100B(L)

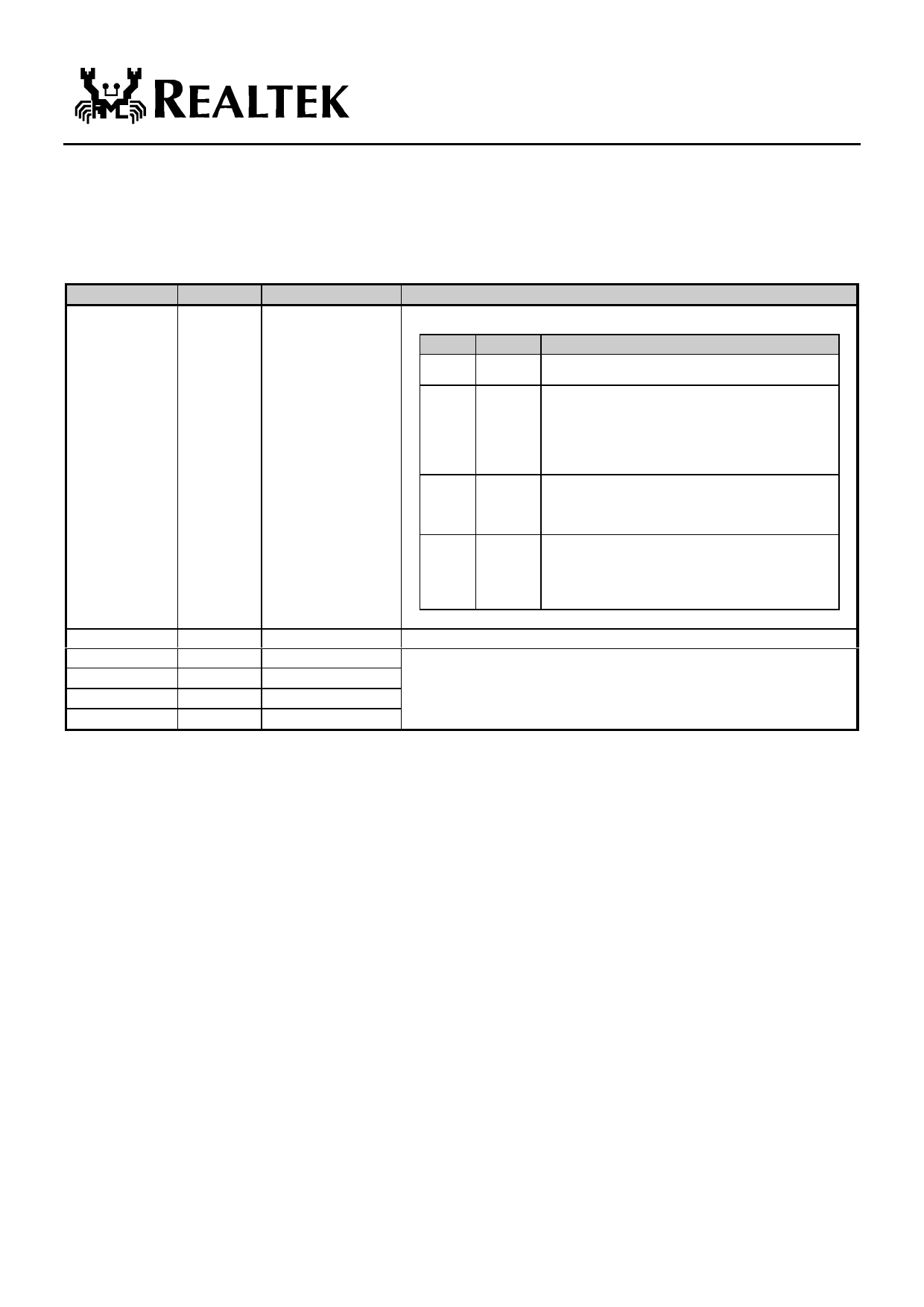

5.9 9346CR: 93C46 Command Register

(Offset 0050h, R/W)

This register is used for issuing commands to the RTL8100B(L). These commands are issued by setting the corresponding bits for

the function. A warm software reset along with individual reset and enable/disable for transmitter and receiver are provided as well.

Bit

R/W

Symbol

Description

7-6

R/W

EEM1-0

Operating Mode: These 2 bits select the RTL8100B(L) operating mode.

EEM1

0

0

1

1

EEM0

0

1

0

1

Operating Mode

Normal: RTL8100B(L) network/host communication

mode.

Auto-load: Entering this mode will make the

RTL8100B(L) load the contents of 93C46 like when the

RSTB signal is asserted. This auto-load operation will take

about 2 ms. After it is completed, the RTL8100B(L) goes

back to the normal mode automatically (EEM1 = EEM0 =

0) and all the other registers are reset to default values.

93C46 Programming: In this mode, both network and

host bus master operations are disabled. The 93C46 can

be directly accessed via bit3-0 which now reflect the

states of EECS, EESK, EEDI, & EEDO pins respectively.

Config Register Write Enable: Before writing to

CONFIG0, 1, 3, 4 registers, and bit13, 12, 8 of

BMCR(offset 62h-63h), the RTL8100B(L) must be

placed in this mode. This will prevent RTL8100B(L)'s

configurations from accidental change.

4-5

-

3

R/W

2

R/W

1

R/W

0

R

-

EECS

EESK

EEDI

EEDO

Reserved

These bits reflect the state of EECS, EESK, EEDI & EEDO pins in

auto-load or 93C46 programming mode.

2001-11-9

19

Rev.1.41