A25L40PMF-50UF Ver la hoja de datos (PDF) - AMIC Technology

Número de pieza

componentes Descripción

Lista de partido

A25L40PMF-50UF Datasheet PDF : 34 Pages

| |||

Release from Deep Power-down and Read Electronic

Signature (RES)

Once the device has entered the Deep Power-down mode, all

instructions are ignored except the Release from Deep

Power-down and Read Electronic Signature (RES) instruction.

Executing this instruction takes the device out of the Deep

Power-down mode.

The instruction can also be used to read, on Serial Data Output

(Q), the 8-bit Electronic Signature, whose value for the

A25L80P is 13h.

Except while an Erase, Program or Write Status Register cycle

is in progress, the Release from Deep Power-down and Read

Electronic Signature (RES) instruction always provides access

to the 8-bit Electronic Signature of the device, and can be

applied even if the Deep Power-down mode has not been

entered.

Any Release from Deep Power-down and Read Electronic

Signature (RES) instruction while an Erase, Program or Write

Status Register cycle is in progress, is not decoded, and has

no effect on the cycle that is in progress.

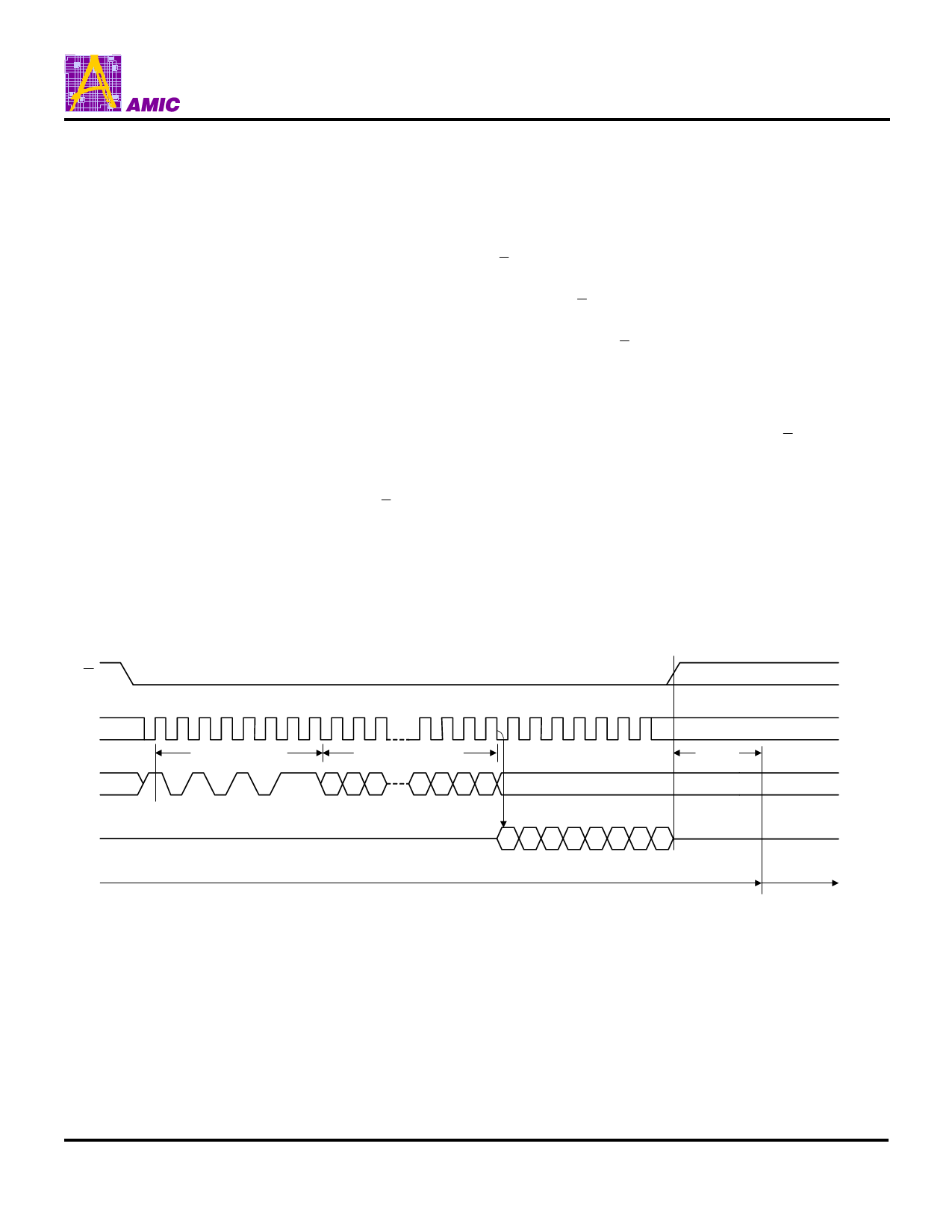

The device is first selected by driving Chip Select ( S ) Low. The

instruction code is followed by 3 dummy bytes, each bit being

A25L80P

latched-in on Serial Data Input (D) during the rising edge of

Serial Clock (C). Then, the 8-bit Electronic Signature, stored in

the memory, is shifted out on Serial Data Output (Q), each bit

being shifted out during the falling edge of Serial Clock (C).

The instruction sequence is shown in Figure 15.

The Release from Deep Power-down and Read Electronic

Signature (RES) instruction is terminated by driving Chip Select

( S ) High after the Electronic Signature has been read at least

once. Sending additional clock cycles on Serial Clock (C), while

Chip Select ( S ) is driven Low, cause the Electronic Signature

to be output repeatedly.

When Chip Select ( S ) is driven High, the device is put in the

Stand-by Power mode. If the device was not previously in the

Deep Power-down mode, the transition to the Stand-by Power

mode is immediate. If the device was previously in the Deep

Power-down mode, though, the transition to the Standby Power

mode is delayed by tRES2, and Chip Select ( S ) must remain

High for at least tRES2 (max), as specified in AC Characteristics

Table . Once in the Stand-by Power mode, the device waits to

be selected, so that it can receive, decode and execute instruc-

tions.

Figure 15. Release from Deep Power-down and Read Electronic Signature (RES) Instruction Sequence and

Data-Out Sequence

S

0 1 2 3 4 5 6 7 8 9 10 28 29 30 31 32 33 34 35 36 37 38

C

Instruction

3 Dummy Butes

D

23 22 21 3 2 1 0

MSB

High Impedance

Q

76543210

MSB

Deep Power-down Mode

Note: The value of the 8-bit Electronic Signature, for the A25L80P, is 13h.

tRES2

Stand-by Mode

PRELIMINARY (May 2005, Version 0.0)

20

AMIC Technology Corp.