AS8201 Ver la hoja de datos (PDF) - austriamicrosystems AG

Número de pieza

componentes Descripción

Lista de partido

AS8201 Datasheet PDF : 13 Pages

| |||

TTP/C-C1 Communications Controller Data Sheet

AS8201

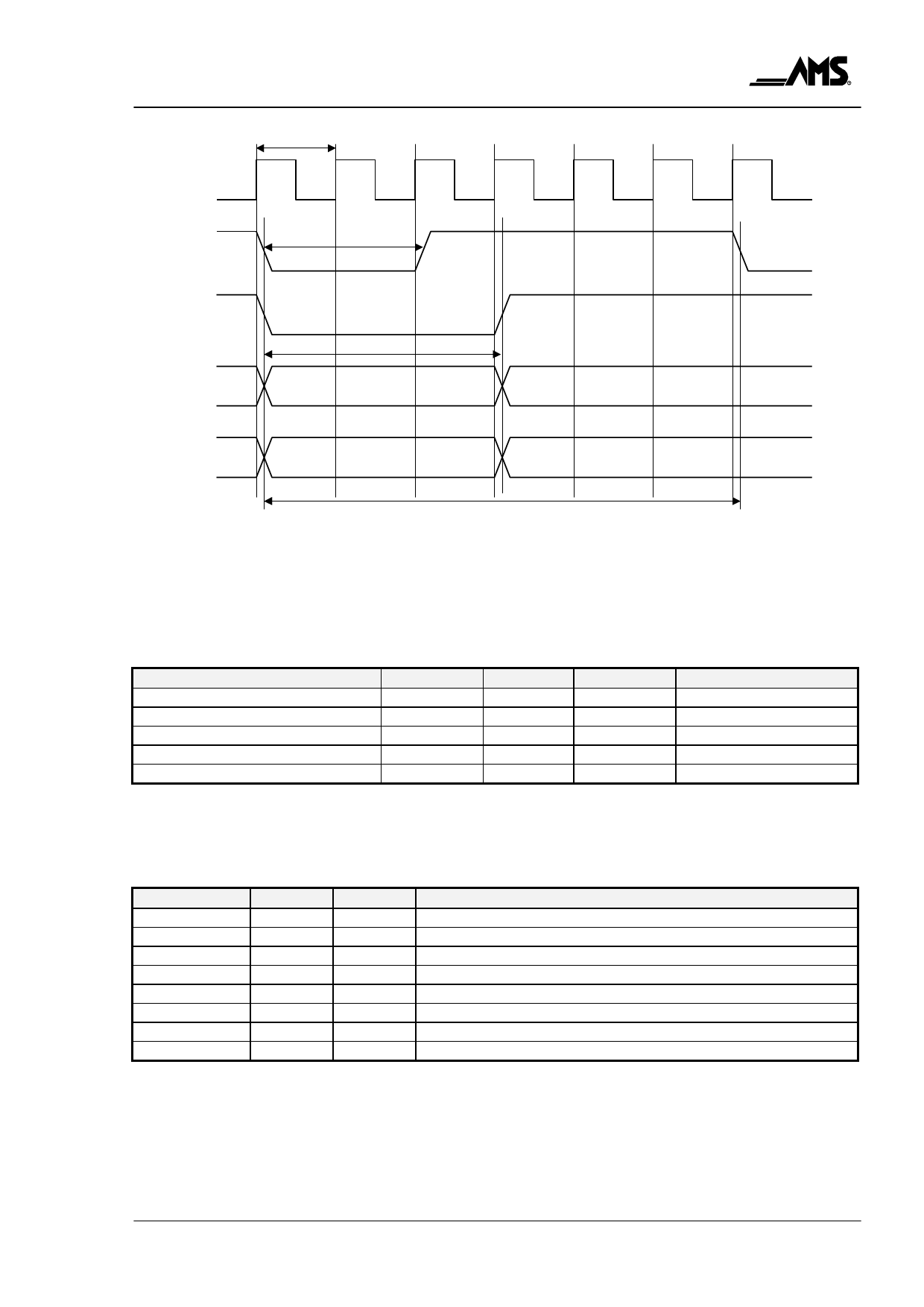

tct

microtick

ram_ceb

ram_web

ram_address

tce

ta

address stable

Austria Mikro Systeme International AG

XXX

ram_data

data stable

trwct

Figure 4: Write Cycle Timing

XXXX

Addresses, data and RAM_WEB have to be stable before the falling edge of RAM_CEB.

RAM_CEB has to be applied for 2 microticks. Addresses, data, and RAM_WEB have to be

applied for 3 microticks.

Parameter

controller cycle time

duration of chip enable

address time

data valid time

read write cycle time

Table 3: Host Interface Timing

Symbol

tct

tce

ta

tdv

trwct

Min

87.5ns

137.5ns

Typ

50ns

100ns

150ns

300ns

300ns

Max

112.5ns

162.5ns

Reset and Oscillator

Pin Name

XIN0

XENA0

XOUT0

XIN1

XOUT1

XENA1

RESETB

MICROTICK

mode

in

in

out

in

out

in

in

out

width

1

1

1

1

1

1

1

1

Comment

controller oscillator input

controller clock enable

controller oscillator output

bus guardian oscillator input

bus guardian oscillator output

bus guardian clock enable

external reset

controller clock (inverted)

Table 4: Reset and Oscillator Ports

External Reset Signal

To issue a reset of the chip the RESETB port has to be driven low for at least 200µs. After

power-up the reset must overlap the build-up time of the oscillator circuit.

Rev. NC, October 1999

Page 9 of 13