BT8110 Ver la hoja de datos (PDF) - Unspecified

Número de pieza

componentes Descripción

Lista de partido

BT8110 Datasheet PDF : 84 Pages

| |||

2.0 Functional Description

2.2 Modes of Operation

Bt8110/8110B

High-Capacity ADPCM Processor

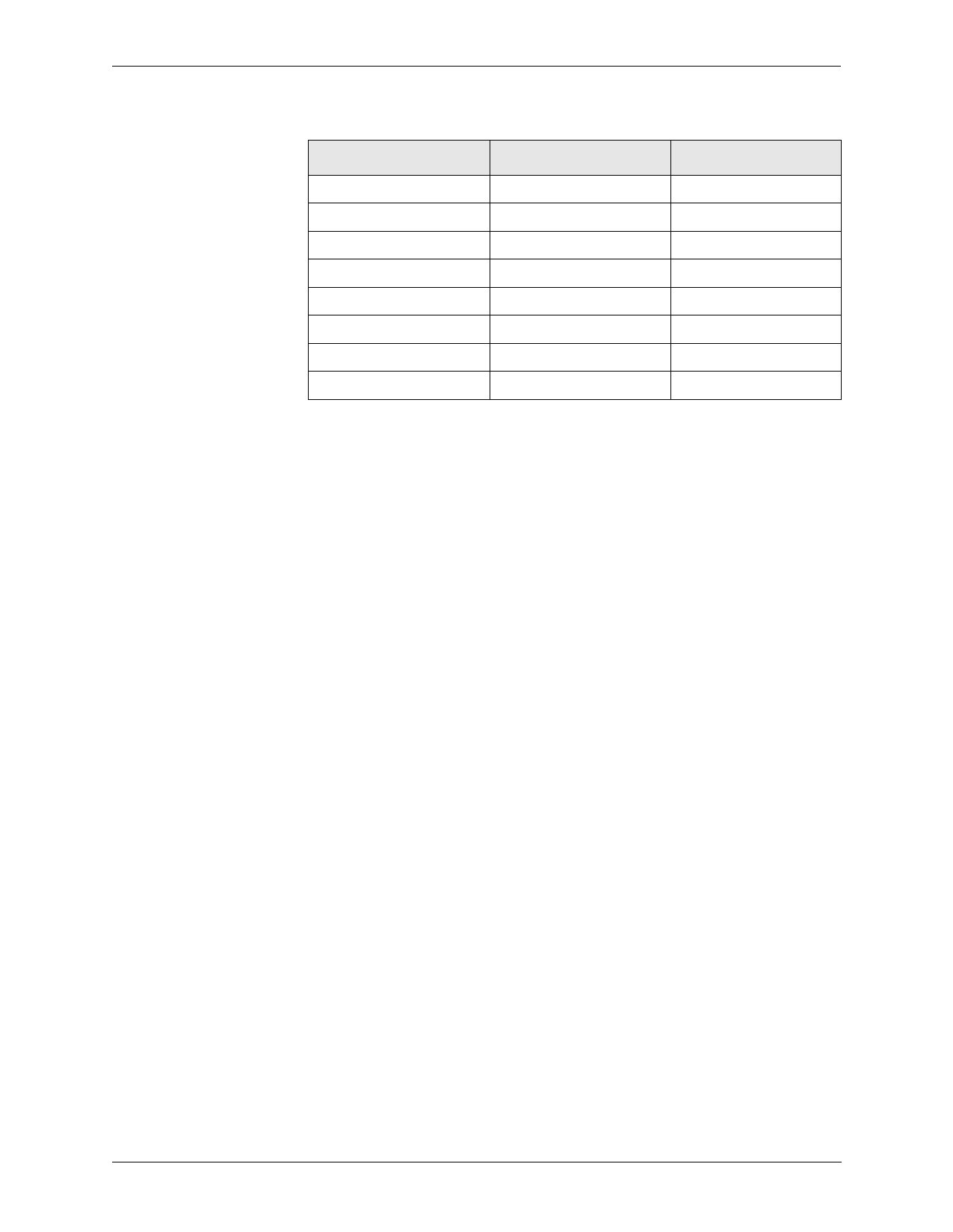

Table 2-3. Parallel Signal Output Bus

Output Bus Bit

Decoder Out

D[7]

Sign Bit

D[6]

Bit 2

D[5]

Bit 3

D[4]

Bit 4

D[3]

Bit 5

D[2]

Bit 6

D[1]

Bit 7

D[0]

Bit 8

Encoder Out

I1

I2

I3

I4

I5

0

0

0

2.2.1.2 Reset Control

The RESET signal pin can be used to reset the algorithm according to ANSI

T1.303–1989 and ITU-T G.726 when microprocessor operation mode is used; the

reset control bit [EN_RST; per_chan_ctrl.5] can also set this function. The

real-time algorithm reset function is useful in Digital Circuit Multiplication

Equipment (DCME), packet-voice, and speech storage applications. The RESET

input is active during the time interval shown in Figure 2-3.

2.2.2 48- or 64-Channel Encoder-Only Operation

Figure 2-4 shows the functional timing for 48- or 64-channel half-duplex

encoder-only operation. The channel numbers in parentheses are for the

48-channel encoder-only mode. The timing is generally the same as for

interleaved timing, but the inputs are all PCM for encoding, and the outputs are

all ADPCM. In this mode of operation, the ADPCM_STB signal occurs once

every 16 clock cycles and the PCM_STB signal is not active. This keeps the

ADPCM_STB signal periodic with both the inputs and the outputs when the

parallel input interface is used.

To operate the Bt8110/8110B in the 48- or 64- channel encoder-only mode,

the Mode Control Register should be set to a value of 0x0D for 64 channels or

0x05 for 48 channels. In many 48-channel configurations, a gapped clock will be

used to account for the frame bit of the T1 signal; this operates correctly as long

as there are exactly 32 clock cycles per channel processed.

The address table for the microprocessor per-channel controls

(encoder/decoder operation only) is given in the Register Summary, Table 3-4.

2-8

Conexant

100060C