DM9106 Ver la hoja de datos (PDF) - Davicom Semiconductor, Inc.

Número de pieza

componentes Descripción

Lista de partido

DM9106 Datasheet PDF : 92 Pages

| |||

DM9106

3-port switch with PCI Interface

1. General Description

The DM9106 is a fully integrated, high performance, and cost-effective fast Ethernet switch controller with

one general PCI bus interface, two ports 10M/100Mbps PHY, and one port MII or RMII interface.

The general PCI bus connects directly to internal host MAC with 32-bit data registers and internal memory. The host

MAC has the similar functions as other 10/100Mbps PHY or MII does. This makes the DM9106 act as an extended four ports

switch and to shorten the latency from PCI port to destination port.

The internal memory of the DM9106 supports up to 1K uni-cast MAC address table, and provides to three

ports’ and PCI port’s transmit and receive buffers. For efficient memory usage algorithm, if application only uses

two ports solution, the another disabled port’s memory resource can be shared to other two ports and PCI port.

Each port of the DM9106 provides four priority transmit queues, that can be defined by port-based, 802.1p

VLAN, or IP packet ToS field automatically, to fit the various bandwidth and latency requirement of data, voice,

and video applications. Each port also supports ingress and/or egress rate control to provide proper bandwidth.

And up to 16 groups of 802.1Q VLAN with Tag/Un-tag functions are supported to provide efficient packet

forwarding.

The TCP/UDP/IPv4 checksum generation and checking functions are also provided by PCI port to offload the

processor computing loading. Besides the packet transmit and receive functions, the PCI port also provides

various registers to control and get status of the DM9106 functional operation. Each port, including the PCI port,

provides the MIB counters and loop-back capability and the build in memory self test (BIST) for system and

board level diagnostic.

The integrated two ports PHY are compliant with IEEE 802.3u standards. The MII interface provides the

flexibility to connect Ethernet PHY, and it can be configured as Reversed MII interface for SoC with MII

interface. An alternative interface, the RMII interface, is also provided to connect the lower pin count Ethernet

PHY or SoC with RMII interface.

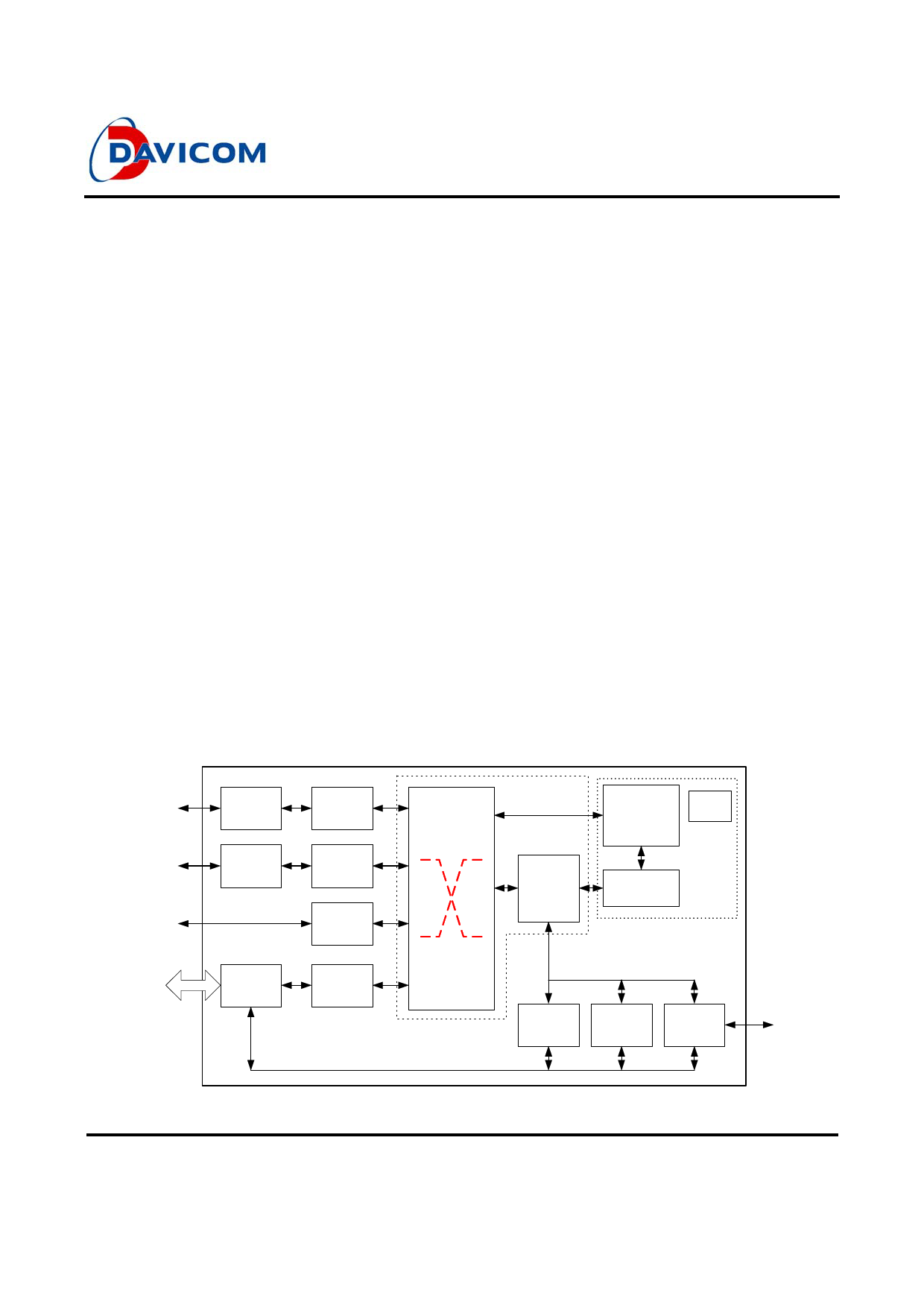

2. Block Diagram

Port 0

MDI/MDIX

Port 1

MDI/MDIX

Port 2

MII / RMII

PCI BUS

10/100M

PHY

10/100M

PHY

Processor

Interface

10/100M

MAC

10/100M

MAC

10/100M

MAC

HOST

MAC

Switch

Fabric

Switch

Engine

Embedded

Memory

Memory

BIST

Switch

Controller

Memory

Management

Control

Registers

MIB

Counters

EEPROM

Interface

EEPROM

8

Preliminary datasheet

DM9106-DS-P01

July 9, 2009