HIP6019B(1998) Ver la hoja de datos (PDF) - Intersil

Número de pieza

componentes Descripción

Lista de partido

HIP6019B Datasheet PDF : 15 Pages

| |||

HIP6019B

Description

Operation

The HIP6019B monitors and precisely controls 4 output

voltage levels (Refer to Figures 1, 2, and 3). It is designed

for microprocessor computer applications with 5V power and

12V bias input from a PS2 or ATX power supply. The IC has

2 PWM controllers, a linear controller, and a linear regulator.

The first PWM controller (PWM1) is designed to regulate the

microprocessor core voltage (VOUT1). PWM1 controller

drives 2 MOSFETs (Q1 and Q2) in a synchronous-rectified

buck converter configuration and regulates the core voltage

to a level programmed by the 5-bit digital-to-analog

converter (DAC). The second PWM controller (PWM2) is

designed to regulate the I/O voltage (VOUT2). PWM2

controller drives a MOSFET (Q3) in a standard buck

converter configuration and regulates the I/O voltage to a

resistor programmable level between 3.0 and 3.5VDC. An

integrated linear regulator supplies the 2.5V clock generator

power (VOUT4). The linear controller drives an external

MOSFET (Q4) to supply the GTL bus power (VOUT3).

Initialization

The HIP6019B automatically initializes upon receipt of input

power. Special sequencing of the input supplies is not

necessary. The Power-On Reset (POR) function continually

monitors the input supply voltages. The POR monitors the

bias voltage (+12VIN) at the VCC pin and the 5V input

voltage (+5VIN) at the OCSET1 pin. The normal level on

OCSET1 is equal to +5VIN less a fixed voltage drop (see

over-current protection). The POR function initiates soft-start

operation after both input supply voltages exceed their POR

thresholds.

Soft-Start

The POR function initiates the soft-start sequence. Initially,

the voltage on the SS pin rapidly increases to approximately

1V (this minimizes the soft-start interval). Then an internal

11µA current source charges an external capacitor (CSS) on

the SS pin to 4V. The PWM error amplifier reference inputs

(+ terminal) and outputs (COMP1 and COMP2 pins) are

clamped to a level proportional to the SS pin voltage. As the

SS pin voltage ramps from 1V to 4V, the output clamp allows

generation of PHASE pulses of increasing width that charge

the output capacitor(s). After this initial stage, the reference

input clamp slows the output voltage rate-of-rise and

provides a smooth transition to the final set voltage.

Additionally, both linear regulator’s reference inputs are

clamped to a voltage proportional to the SS pin voltage. This

method provides a rapid and controlled output voltage rise.

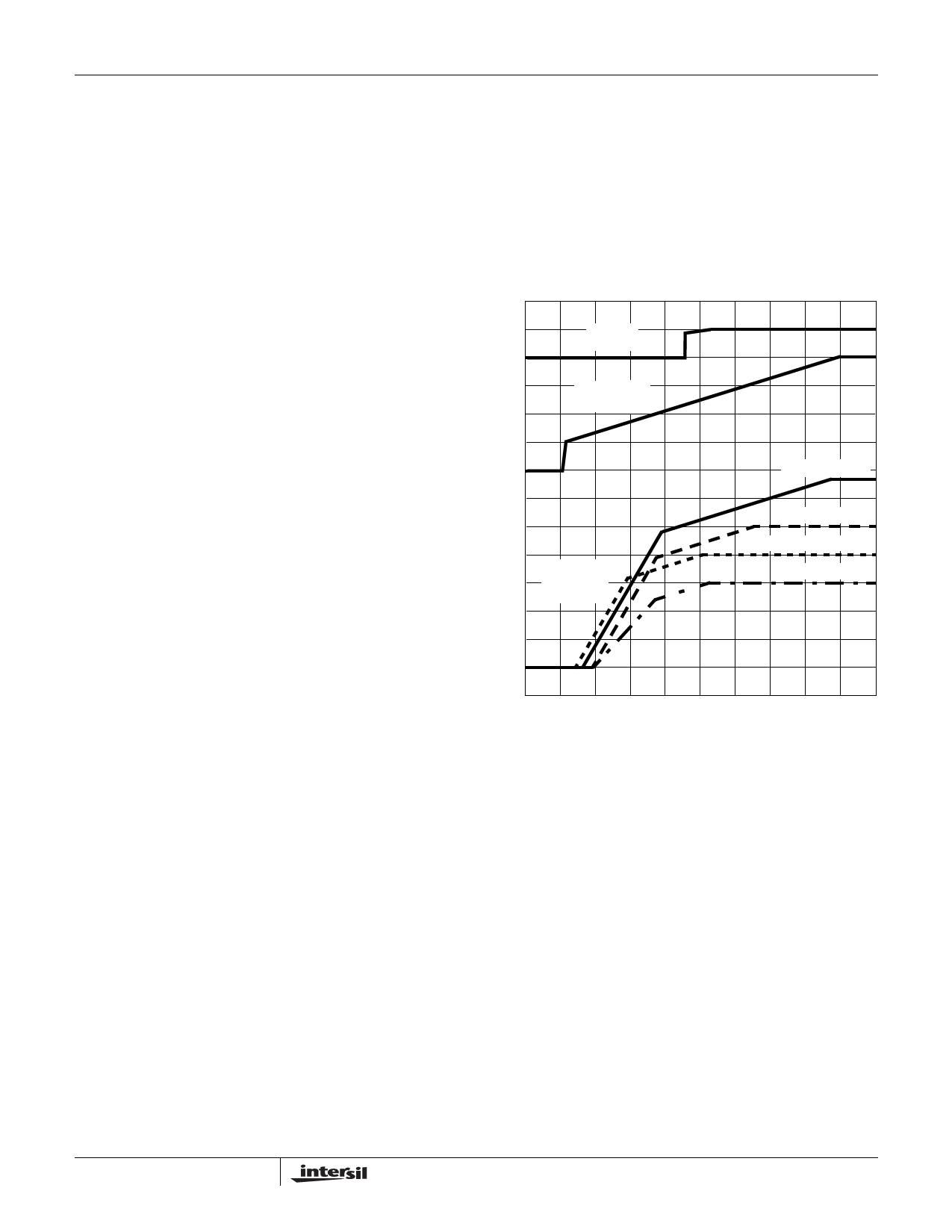

Figure 6 shows the soft-start sequence for the typical

application. At T0 the SS voltage rapidly increases to

approximately 1V. At T1, the SS pin and error amplifier output

voltage reach the valley of the oscillator’s triangle wave. The

oscillator’s triangular waveform is compared to the clamped

error amplifier output voltage. As the SS pin voltage

increases, the pulse-width on the PHASE pin increases. The

interval of increasing pulse-width continues until each output

reaches sufficient voltage to transfer control to the input

reference clamp. If we consider the 3.3V output (VOUT2) in

Figure 6, this time occurs at T2. During the interval between

T2 and T3, the error amplifier reference ramps to the final

value and the converter regulates the output to a voltage

proportional to the SS pin voltage. At T3 the input clamp

voltage exceeds the reference voltage and the output voltage

is in regulation.

PGOOD

(2V/DIV)

0V

SOFT-START

(1V/DIV)

0V

OUTPUT

VOLTAGES

(0.5V/DIV)

VOUT2 ( = 3.3V)

VOUT4 ( = 2.5V)

VOUT1 (DAC = 2V)

VOUT3 ( = 1.5V)

0V

T0 T1

T2

T3

TIME

FIGURE 6. SOFT-START INTERVAL

The remaining outputs are also programmed to follow the

SS pin voltage. Each linear output (VOUT3 and VOUT4)

initially follows the 3.3V output (VOUT2). When each output

reaches sufficient voltage the input reference clamp slows

the rate of output voltage rise. The PGOOD signal toggles

‘high’ when all output voltage levels have exceeded their

under-voltage levels. See the Soft-Start Interval section

under Applications Guidelines for a procedure to determine

the soft-start interval.

Fault Protection

All four outputs are monitored and protected against extreme

overload. A sustained overload on any linear regulator

output or an over-voltage on the PWM outputs disables all

converters and drives the FAULT/RT pin to VCC.

Figure 7 shows a simplified schematic of the fault logic. An

over-voltage detected on either VSEN1 or VSEN2

immediately sets the fault latch. A sequence of three over-

current fault signals also sets the fault latch. A comparator

273