ICS9248-136 Ver la hoja de datos (PDF) - Integrated Circuit Systems

Número de pieza

componentes Descripción

Lista de partido

ICS9248-136 Datasheet PDF : 16 Pages

| |||

Integrated

Circuit

Systems, Inc.

ICS9248-136

Advance Information

Frequency Generator & Integrated Buffers for K7 Processor

Recommended Application:

Single chip clock solution for SIS 730S K7 chipset.

Output Features:

• 1 - Differential pair open drain CPU clock

• 1 - Single-ended open drain CPU clock

• 13 - SDRAM @ 3.3V

• 6- PCI @3.3V,

• 2 - AGP @ 3.3V

• 1- 48MHz, @3.3V fixed.

• 1- 24/48MHz, @3.3V selectable by I2C

(Default is 24MHz)

• 2- REF @3.3V, 14.318MHz.

Features:

• Up to 166MHz frequency support

• Support FS0-FS3 trapping status bit for I2C read back.

• Support power management: CPU, PCI, SDRAM stop

and Power down Mode from I2C programming.

• Spread spectrum for EMI control (0 to -0.5%, ± 0.25%).

• Uses external 14.318MHz crystal

Skew Specifications:

• CPU - CPU: < 175ps

• SDRAM - SDRAM < 250ps

• PCI - PCI: < 500ps

• CPU - SDRAM: < 500ps

• CPU (early) - PCI: 1-4ns (typ. 2ns)

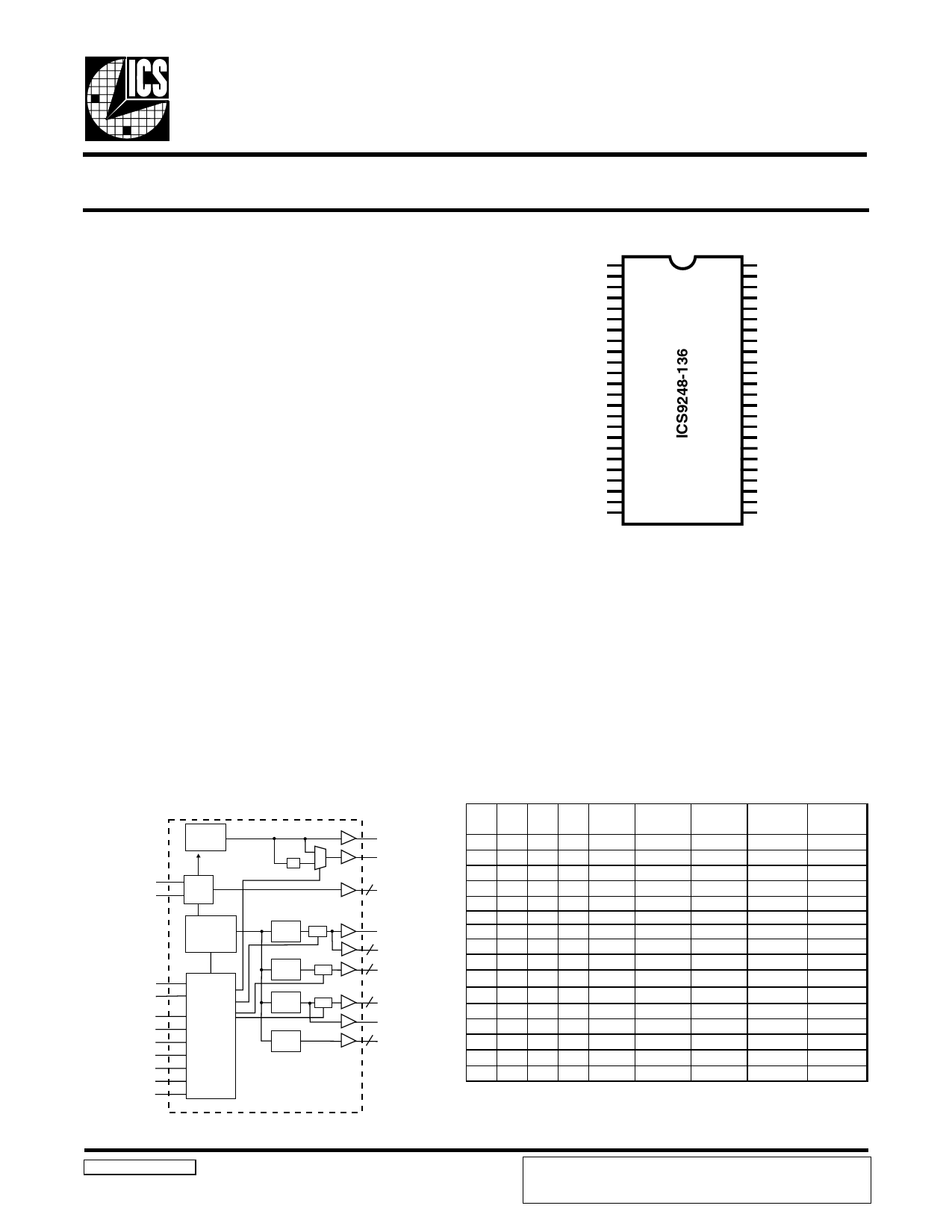

Pin Configuration

VDDA

1

1*(AGPSEL)REF1

2

1*(FS3)REF0

3

GND

4

X1

5

X2

6

VDDPCI

7

*(FS1)PCICLK_F

8

*(FS2)PCICLK0

9

PCICLK1

10

PCICLK2

11

PCICLK3

12

PCICLK4

13

GND

14

VDDAGP

15

AGPCLK0

16

AGPCLK1

17

GND

18

GND

19

*(FS0)48MHz

20

*(MODE)24_48MHz

21

VDD48

22

SDATA

23

SCLK

24

48 VDDCPU

47 CPUCLKT0

46 CPUCLKC0

45 CPUCLKT1

44 GND

43 VDDSDR

42 SDRAM0

41 SDRAM1

40 SDRAM2

39 GND

38 SDRAM3

37 SDRAM4

36 SDRAM5

35 VDDSDR

34 SDRAM6

33 SDRAM7

32 GND

31 SDRAM8/PD#

30 SDRAM9/SDRAM_STOP#

29 GND

28 SDRAM10/PCI_STOP#

27 SDRAM11/CPU_STOP#

26 SDRAM12

25 VDDSDR

48-Pin 300mil SSOP

* These inputs have a 120K pull down to GND.

1 These are double strength.

Block Diagram

PLL2

X1

XTAL

X2

OSC

PLL1

Spread

Spectrum

SDATA

SCLK

FS (3:0)

PD#

PCI_STOP#

CPU_STOP#

SDRAM_STOP#

MODE

AGP_SEL

Control

Logic

Config.

Reg.

/2

CPU

DIVDER

Stop

SDRAM

DIVDER

Stop

PCI

DIVDER

Stop

AGP

DIVDER

Functionality

48MHz

24_48MHz

REF (1:0)

2

CPUCLKC0

CPUCLKT (1:0)

2

SDRAM (12:0)

13

PCICLK (4:0)

5

PCICLK_F

AGP (1:0)

2

FS3 FS2 FS1 FS0 CPU SDRAM

0 0 0 0 100.00 100.00

0 0 0 1 100.00 133.33

0 0 1 0 100.00 150.00

0 0 1 1 100.00 66.67

0 1 0 0 112.00 112.00

0 1 0 1 125.00 100.00

0 1 1 0 124.00 124.00

0 1 1 1 133.33 100.00

1 0 0 0 133.33 133.33

1 0 0 1 150.00 150.00

1 0 1 0 111.11 166.67

1 0 1 1 110.00 165.00

1 1 0 0 166.67 166.67

1 1 0 1 90.00 90.00

1 1 1 0 48.00 48.00

1 1 1 1 45.00 60.00

P CICLK

33.33

33.33

30.00

33.33

33.60

31.25

31.00

33.33

33.33

30.00

33.33

33.00

33.33

30.00

32.00

30.00

AGP

SEL = 0

66.67

66.67

60.00

66.67

67.20

62.50

62.00

66.67

66.67

60.00

66.67

66.00

66.67

60.00

64.00

60.00

AGP

SEL = 1

50.00

50.00

50.00

50.00

56.00

50.00

46.50

50.00

50.00

50.00

55.56

55.00

55.56

45.00

48.00

45.00

9248-136 Rev - 03/29/01

Third party brands and names are the property of their respective owners.

ADVANCE INFORMATION documents contain information on products

in the formative or design phase development. Characteristic data and

other specifications are design goals. ICS reserves the right to change or

discontinue these products without notice.