AV9248-73 Ver la hoja de datos (PDF) - Integrated Circuit Systems

Número de pieza

componentes Descripción

Lista de partido

AV9248-73 Datasheet PDF : 15 Pages

| |||

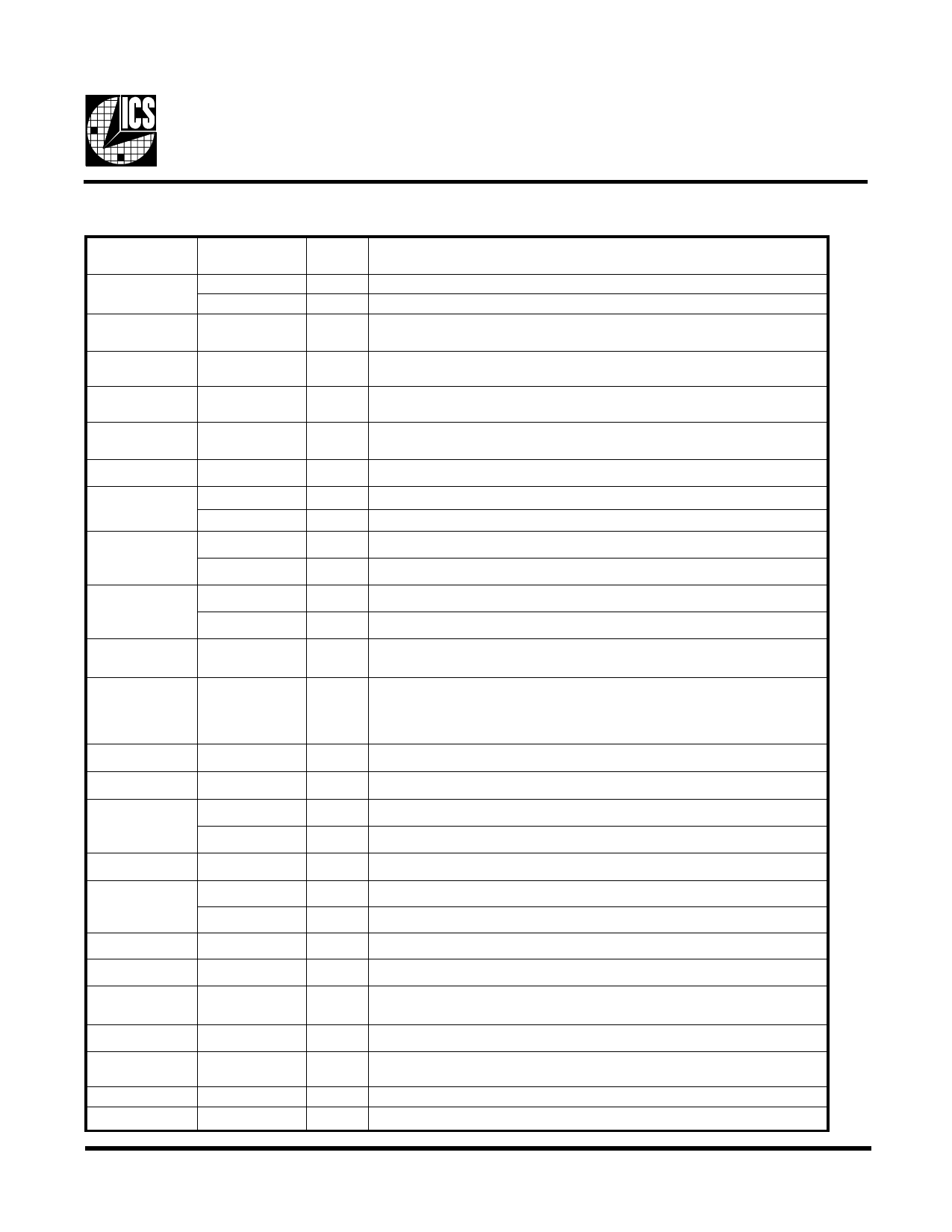

ICS9248 - 73

Pin Descriptions

PIN

NUMBER

1

2, 9, 10,

18, 25, 30, 38

PIN NAME

SEL_3V66

REF0

VDD

3

X1

4

5, 6, 14, 21,

29, 42, 34,

7, 8

11

12

13

15, 16, 17,

19, 20

X2

GND

3V66 (0:1)

PCICLK0

FS0

PCICLK1

FS1

PCICLK2

SEL24_48#

PCICLK (3:7)

22

PD#

23

SCLK

24

SDATA

48MHz

26

FS3

27

48MHz

24_48MHz

28

FS2

29

GND48

31

41, 40, 39, 37,

36, 35, 33, 32,

43

SDRAM_F

SDRAM (0:7)

GNDL

45, 44

47

48, 46

CPUCLK (0:1)

IOAPIC

VDDL

TYPE

DESCRIPTION

IN This pin selects the 3V66 output frequency.

OUT 3.3V, 14.318MHz reference clock output.

PWR 3.3V power supply

IN

OUT

Crystal input, has internal load cap (33pF) and feedback

resistor from X2

Crystal output, nominally 14.318MHz.

Has internal load cap (33pF)

PWR Ground pins for 3.3V supply

OUT

OUT

IN

OUT

IN

OUT

IN

3.3V clock outputs for HUB running at 2XPCI MHz

3.3V PCI clock outputs, with Synchronous CPUCLKS

Logic input frequency select bit. Input latched at power on.

3.3V PCI clock outputs, with Synchronous CPUCLKS

Logic input frequency select bit. Input latched at power on.

3.3V PCI clock outputs, with Synchronous CPUCLKS

Logic input to select output.

OUT 3.3V PCI clock outputs, with Synchronous CPUCLKS

Asynchronous active low input pin used to power down the device into

IN

a low power state. The internal clocks are disabled and the VCO and

the crystal are stopped. The latency of the power down will not be

greater than 3ms.

IN Clock input of I2C input

IN Data input for I2C serial input.

OUT 3.3V Fixed 48MHz clock output for USB

IN Logic input frequency select bit. Input latched at power on.

OUT 3.3V Fixed 48MHz clock output for USB

OUT 24 or 48MHz output controlled by SEL24_48#.

IN Logic input frequency select bit. Input latched at power on.

PWR

OUT

OUT

PWR

OUT

OUT

PWR

Ground for 48MHz outputs

3.3V free running 100MHz SDRAM not affected by I2C

3.3V output running 100MHz. All SDRAM outputs can be turned off

through I2C

Ground for 2.5V power supply for CPU & APIC

2.5V Host bus clock output, up to 150MHz depending on FS (0:3)

pins Refer page 3.

2.5V clock outputs running at PCI/2 MHz.

2.5V power suypply for CPU, IOAPIC

2