8405202QA Ver la hoja de datos (PDF) - Intersil

Número de pieza

componentes Descripción

Lista de partido

8405202QA Datasheet PDF : 37 Pages

| |||

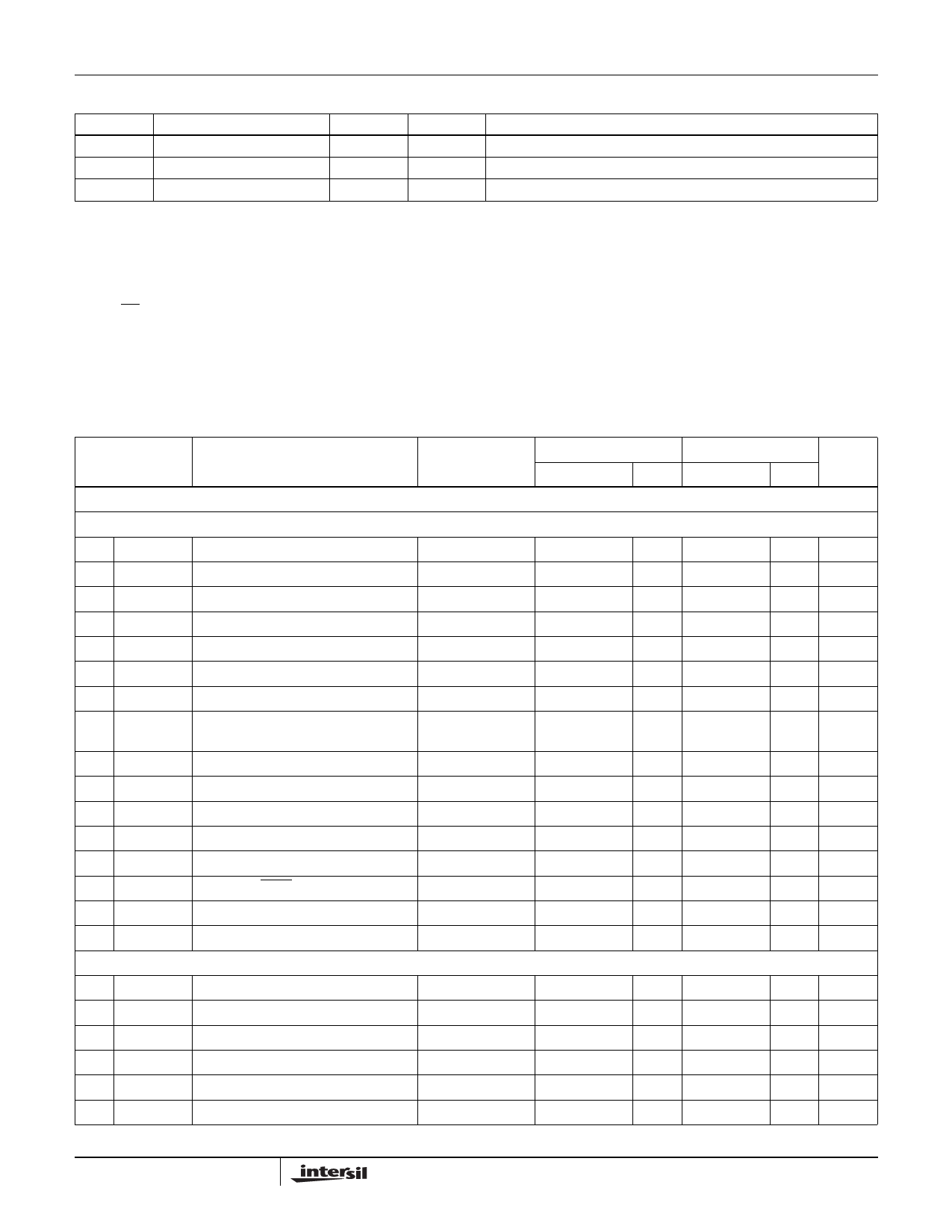

80C86

Capacitance

TA = +25°C

SYMBOL

PARAMETER

TYPICAL

UNITS

TEST CONDITIONS

CIN

COUT

CI/O

NOTES:

Input Capacitance

Output Capacitance

I/O Capacitance

25

pF

FREQ = 1MHz. All measurements are referenced to device GND

25

pF

FREQ = 1MHz. All measurements are referenced to device GND

25

pF

FREQ = 1MHz. All measurements are referenced to device GND

3. lBHH should be measured after raising VIN to VCC and then lowering to 3.0V on the following pins 2-16, 26-32, 34-39.

4. IBHL should be measured after lowering VIN to GND and then raising to 0.8V on the following pins: 2-16, 34-39.

5. lCCSB tested during clock high time after halt instruction executed. VIN = VCC or GND, VCC = 5.5V, Outputs unloaded.

6. IO should be measured by putting the pin in a high impedance state and then driving VOUT to GND on the following pins: 26-29 and 32.

7. MN/MX is a strap option and should be held to VCC or GND.

AC Electrical Specifications

VCC = 5.0V ±10%; TA = 0°C to +70°C (C80C86, C80C86-2)

VCC = 5.0V ±100%; TA = -55°C to +125°C (M80C86)

VCC = 5.0V ±5%; TA = -55°C to +125°C (M80C86-2). Parameters with MIN and/or MAX limits are 100%

tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are

not production tested.

SYMBOL

PARAMETER

TEST

CONDITIONS

80C86

MIN

MAX

80C86-2

MIN

MAX

UNITS

MINIMUM COMPLEXITY SYSTEM

Timing Requirements

(1)

TCLCL Cycle Period

200

125

ns

(2) TCLCH CLK Low Time

118

68

ns

(3) TCHCL CLK High Time

69

44

ns

(4) TCH1CH2 CLK Rise Time

From 1.0V to 3.5V

10

10

ns

(5) TCL2C1 CLK FaIl Time

From 3.5V to 1.0V

10

10

ns

(6)

TDVCL Data In Setup Time

30

20

ns

(7) TCLDX1 Data In Hold Time

10

10

ns

(8) TR1VCL RDY Setup Time into 82C84A

(Notes 8, 9)

35

35

ns

(9) TCLR1X RDY Hold Time into 82C84A (Notes 8, 9)

0

0

ns

(10) TRYHCH READY Setup Time into 80C86

118

68

ns

(11) TCHRYX READY Hold Time into 80C86

30

20

ns

(12) TRYLCL READY Inactive to CLK (Note 10)

-8

-8

ns

(13) THVCH HOLD Setup Time

35

20

ns

(14) TINVCH lNTR, NMI, TEST Setup Time (Note 9)

30

15

ns

(15)

TILIH Input Rise Time (Except CLK)

From 0.8V to 2.0V

15

15

ns

(16)

TIHIL Input FaIl Time (Except CLK)

From 2.0V to 0.8V

15

15

ns

Timing Responses

(17) TCLAV Address Valid Delay

(18) TCLAX Address Hold Time

(19) TCLAZ Address Float Delay

(20) TCHSZ Status Float Delay

(21) TCHSV Status Active Delay

(22) TLHLL ALE Width

CL = 100pF

CL = 100pF

CL = 100pF

CL = 100pF

CL = 100pF

CL = 100pF

10

110

10

60

ns

10

10

ns

TCLAX

80

TCLAX

50

ns

80

50

ns

10

110

10

60

ns

TCLCH - 20

TCLCH - 10

ns

18

FN2957.3

January 9, 2009