IDT72805LB Ver la hoja de datos (PDF) - Integrated Device Technology

Número de pieza

componentes Descripción

Lista de partido

IDT72805LB

IDT72805LB Datasheet PDF : 26 Pages

| |||

IDT72805LB/72815LB/72825LB/72845LB CMOS Dual SyncFIFOTM

256 x 18, 512 x 18, 1,024 x 18, and 4,096 x 18

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

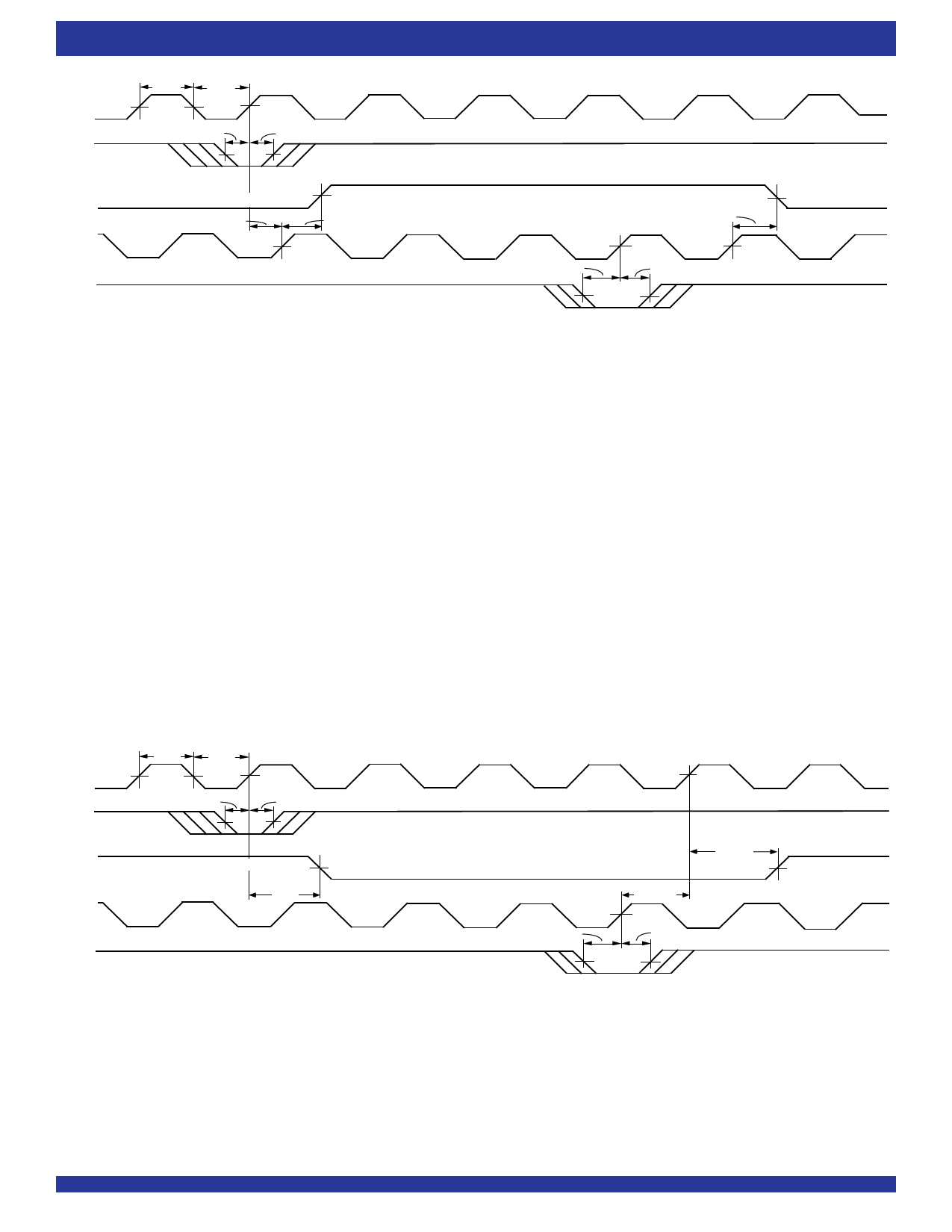

WCLK

WEN

tCLKH

tCLKL

tENS

tENH

PAE

RCLK

REN

n words in FIFO(2),

n + 1words in FIFO(3)

tSKEW2 (4)

tPAES

n + 1 words in FIFO(2),

n + 2 words in FIFO(3)

tENS

tPAES

tENH

n Words in FIFO(2),

n + 1 words in FIFO(3)

3139 drw 22

NOTES:

1. n = PAE offset.

2. For IDT Standard Mode.

3. For FWFT Mode.

4. tSKEW2 is the minimum time between a rising WCLK edge and a rising RCLK edge for PAE to go HIGH during the current clock cycle. If the time between the rising edge of WCLK and the

rising edge of RCLK is less than tSKEW2, then the PAE deassertion may be delayed one extra RCLK cycle.

5. PAE is asserted and updated on the rising edge of RCLK only.

6. Select this mode by setting (FL, RXI, WXI) = (1,0,0), (1,0,1), or (1,1,0) during Reset.

Figure 22. Synchronous Programmable Almost-Empty Flag Timing (IDT Standard and FWFT Modes)

WCLK

WEN

PAF

RCLK

REN

tCLKH

tCLKL

tENS

tENH

D-(m+1) Words in FIFO

tPAFS

D - m Words in FIFO

tENS

tSKEW2(3)

tENH

tPAFS

D -(m+1) Words

in FIFO

3139 drw 23

NOTES:

1. m = PAF offset.

2. D = maximum FIFO Depth.

In IDT Standard Mode: D = 256 for the IDT72805, 512 for the IDT72815, 1,024 for the IDT72825 and 4,096 for the IDT72845.

In FWFT Mode: D = 257 for the IDT72805, 513 for the IDT72815, 1,025 for the IDT72825 and 4,097 for the IDT72845.

3. tSKEW2 is the minimum time between a rising RCLK edge and a rising WCLK edge for PAF to go HIGH during the current clock cycle. If the time between the rising edge of RCLK and

the rising edge of WCLK is less than tSKEW2, then the PAF deassertion time may be delayed an extra WCLK cycle.

4. PAF is asserted and updated on the rising edge of WCLK only.

5. Select this mode by setting (FL, RXI, WXI) = (1,0,0), (1,0,1), or (1,1,0) during Reset.

Figure 23. Synchronous Programmable Almost-Full Flag Timing (IDT Standard and FWFT Modes)

20