IDT72815LB35BG Ver la hoja de datos (PDF) - Integrated Device Technology

Número de pieza

componentes Descripción

Lista de partido

IDT72815LB35BG

IDT72815LB35BG Datasheet PDF : 20 Pages

| |||

IDT72805/72815/72825 CMOS Dual SyncFIFO™

256 x 18, 512 x 18, and 1024 x 18

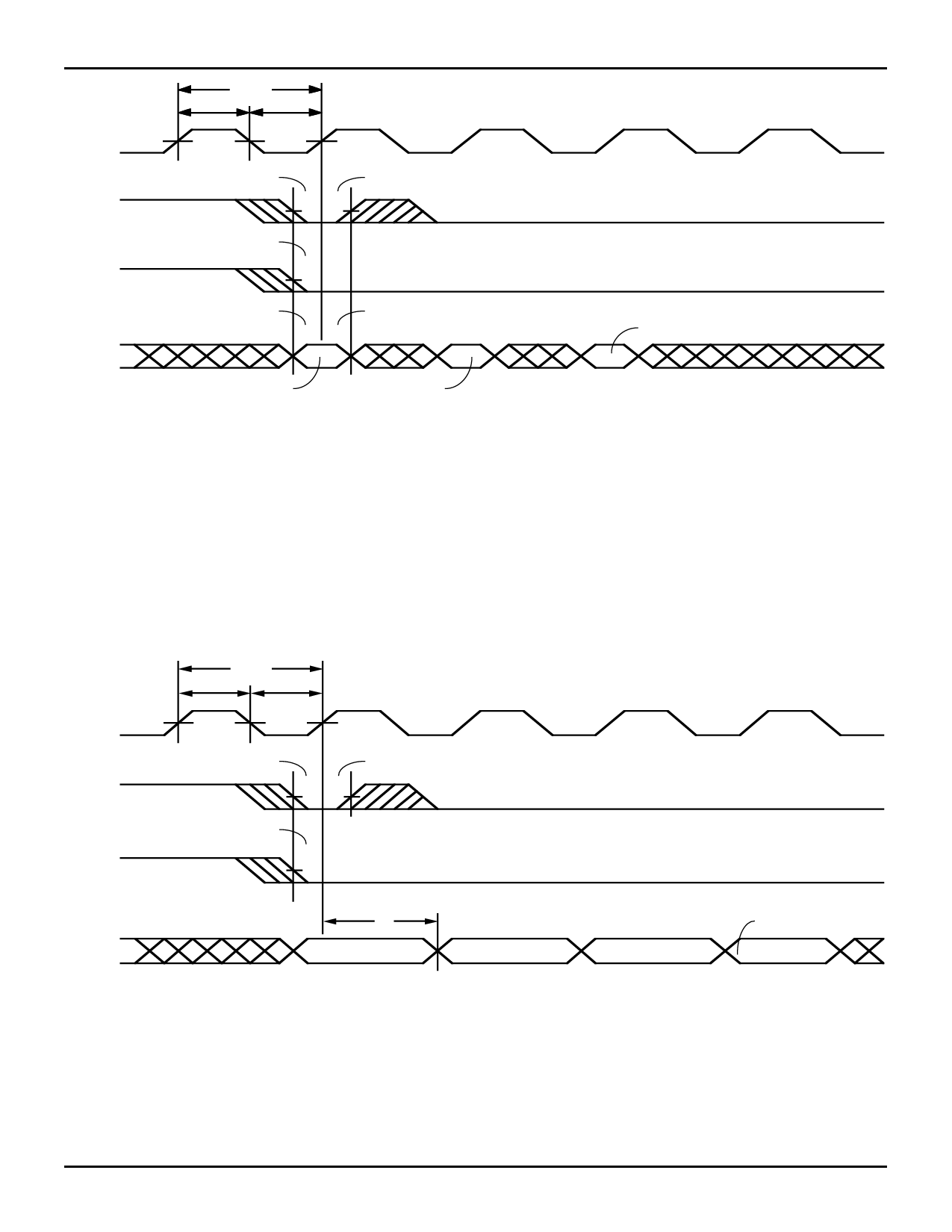

tCLKH

tCLK

tCLKL

WCLK

tENS

tENH

LD

tENS

COMMERCIAL TEMPERATURE RANGE

WEN

D0–D15

tDS

PAE OFFSET

tDH

PAE OFFSET

PAF OFFSET

D0–D11

Figure 10. Write Programmable Registers

3139 drw 10

RCLK

tCLKH

LD

REN

Q0–Q15

tCLK

tCLKL

tENS

tENH

tENS

tA

UNKNOWN

PAE OFFSET

PAF OFFSET

PAE OFFSET

3139 drw 11

Figure 11. Read Programmable Registers

5.17

14