LAN91C100-FD Ver la hoja de datos (PDF) - SMSC -> Microchip

Número de pieza

componentes Descripción

Lista de partido

LAN91C100-FD Datasheet PDF : 78 Pages

| |||

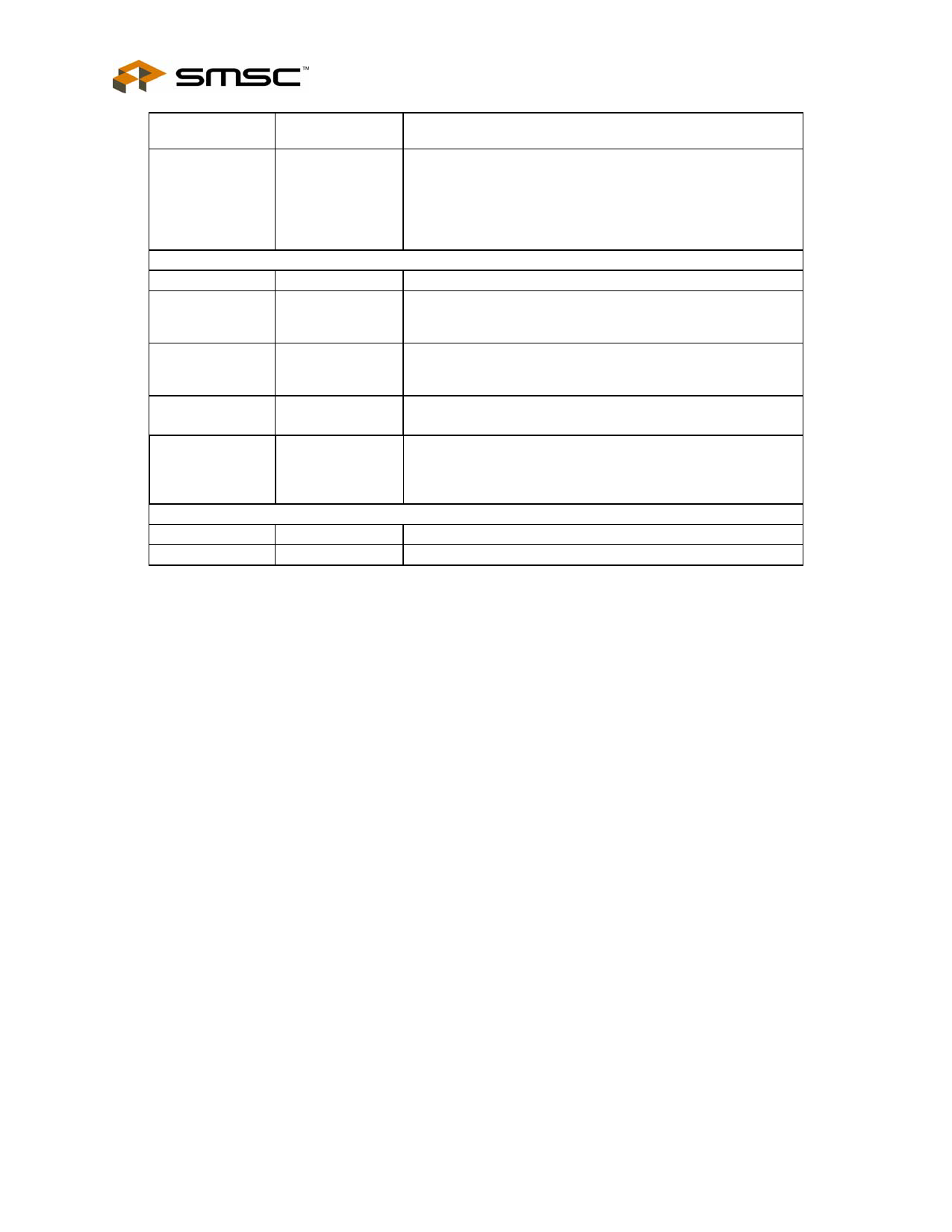

FEAST Fast Ethernet Controller with Full Duplex Capability

EISA BUS

SIGNAL

LAN91C100FD

SIGNAL

NOTES

nEX32

nNOWS

(optional

additional logic)

nLDEV

nLDEV is a totem pole output. nLDEV is active on valid

decodes of LAN91C100FD pins A15-A4, and AEN=0.

nNOWS is similar to nLDEV except that it should go inactive

on nSTART rising. nNOWS can be used to request

compressed cycles (1.5 BCLK long, nRD/nWR will be 1/2

BCLK wide).

THE FOLLOWING SIGNALS SUPPORT SLAVE DMA TYPE "C" BURST CYCLES

BCLK

LCLK

EISA Bus Clock. Data transfer clock for DMA bursts.

nDAK<n>

nDATACS

DMA Acknowledge. Active during Slave DMA cycles. Used

by the LAN91C100FD as nDATACS direct access to data

path.

nIORC

W/nR

Indicates the direction and timing of the DMA cycles. High

during LAN91C100FD writes, low during LAN91C100FD

reads.

nIOWC

nCYCLE

Indicates slave DMA writes.

nEXRDY

VCC

GND

nRDYRTN

nVLBUS

A1

EISA bus signal indicating whether a slave DMA cycle will

take place on the next BCLK rising edge, or should be

postponed. nRDYRTN is used as an input in the slave DMA

mode to bring in EXRDY.

UNUSED PINS

Rev. 01-20-06

Page 62

DATASHEET

SMSC DS – LAN91C100FD Rev. D