PCA9561 Ver la hoja de datos (PDF) - Philips Electronics

Número de pieza

componentes Descripción

Lista de partido

PCA9561 Datasheet PDF : 17 Pages

| |||

Philips Semiconductors

Quad 6-bit multiplexed I2C EEPROM DIP switch

Product data sheet

PCA9561

FEATURES

• Selection of non-volatile register_n as source to MUX_OUT pins

via I2C-bus

• I2C-bus can override MUX_SELECT pin in selecting output

source

• 6-bit 5-to-1 multiplexer DIP switch

• 4 internal non-volatile registers

• Internal non-volatile registers programmable and readable via

I2C-bus

• 6 open drain multiplexed outputs

• 400 kHz maximum clock frequency

• Operating supply voltage 3.0 V to 3.6 V

• 5 V and 2.5 V tolerant inputs/outputs

• Useful for Speed Step® configuration of laptop

• 2 address pins, allowing up to 4 devices on the I2C-bus

• MUX_IN values readable via I2C-bus

• ESD protection exceeds 200 V HBM per JESD22-A114, 200 V

MM per JESD22-A115, and 1000 V CDM per JESD22-C101

• Latch-up testing is done to JESDEC Standard JESD78 which

exceeds 100 mA.

DESCRIPTION

The PCA9561 is a 20-pin CMOS device consisting of four 6-bit

non-volatile EEPROM registers, 6 hardware pin inputs and a 6-bit

multiplexed output. It is used for DIP switch-free or jumper-less

system configuration and supports Mobile and Desktop VID

Configuration, where 5 preset values (4 sets of internal non-volatile

registers and 1 set of external hardware pins) set processor voltage

for operation in various performance or battery conservation sleep

modes. The PCA9561 is also useful in server and

telecom/networking applications when used to replace DIP switches

or jumpers, since the settings can be easily changed via I2C/SMBus

without having to power down the equipment to open the cabinet.

The non-volatile memory retains the most current setting selected

before the power is turned off.

The PCA9561 typically resides between the CPU and Voltage

Regulator Module (VRM) when used for CPU VID (Voltage

IDentification code) configuration. It is used to bypass the

CPU-defined VID values and provide a different set of VID values to

the VRM, if an increase in the CPU voltage is desired. An increase

in CPU voltage combined with an increase in CPU frequency leads

to a performance boost of up to 7.5%. Lower CPU voltage reduces

power consumption. The main advantage of the PCA9561 over

older devices, such as the PCA9559 or PCA9560, is that it contains

four internal non-volatile EEPROM registers instead of just one or

two, allowing five independent settings which allows a more

accurate CPU voltage tuning depending on specific applications.

The PCA9561 has 2 address pins, allowing up to 4 devices to be

placed on the same I2C-bus or SMBus.

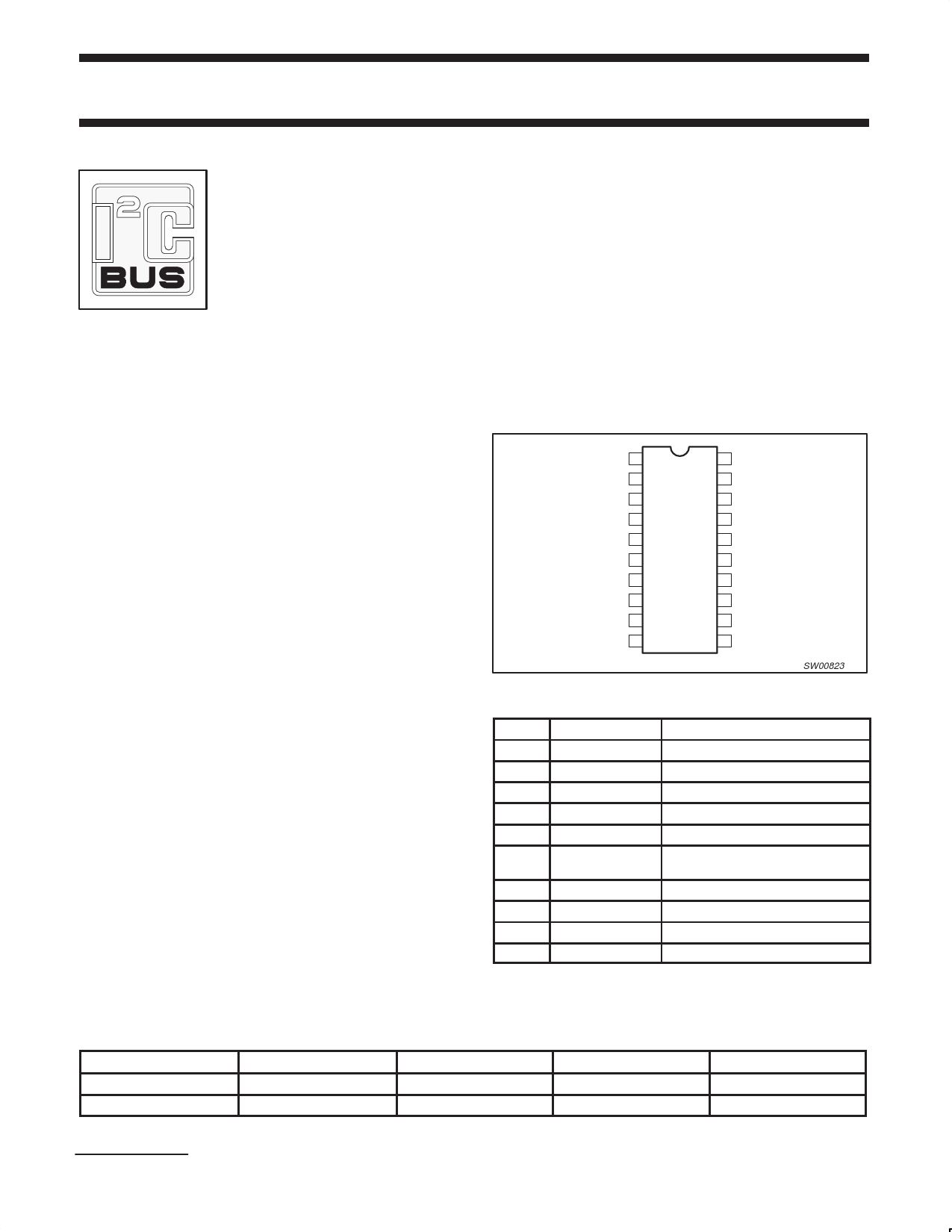

PIN CONFIGURATION

SCL 1

SDA 2

A0 3

MUX_IN_A 4

MUX_IN_B 5

MUX_IN_C 6

MUX_IN_D 7

MUX_IN_E 8

MUX_IN_F 9

GND 10

20 VDD

19 WP

18 A1

17 MUX_OUT_A

16 MUX_OUT_B

15 MUX_OUT_C

14 MUX_OUT_D

13 MUX_OUT_E

12 MUX_OUT_F

11 MUX_SELECT

SW00823

PIN DESCRIPTION

PIN

SYMBOL

1

I2C SCL

2

I2C SDA

3

A0

4–9

MUX_IN_A–F

10

GND

11

MUX_SELECT

12–17

18

19

20

MUX_OUT_F–A

A1

WP

VDD

FUNCTION

Serial I2C-bus clock

Serial bi-directional I2C-bus data

A0 address

External inputs to multiplexer

Ground

Selects MUX_IN inputs or register

contents for MUX_OUT outputs

Open drain multiplexed outputs

A1 address

Non-volatile register write-protect

Power supply: +3.0 to +3.6 V

ORDERING INFORMATION

PACKAGES

20-Pin Plastic SO

20-Pin Plastic TSSOP

TEMPERATURE RANGE

–40 to +85 °C

–40 to +85 °C

ORDER CODE

PCA9561D

PCA9561PW

TOPSIDE MARK

PCA9561D

PCA9561

Standard packing quantities and other packaging data is available at www.philipslogic.com/packaging.

® Speed Step is a registered trademark of Intel Corp.

2004 May 17

2

DRAWING NUMBER

SOT163-1

SOT360-1