PEB20954(1999) Ver la hoja de datos (PDF) - Infineon Technologies

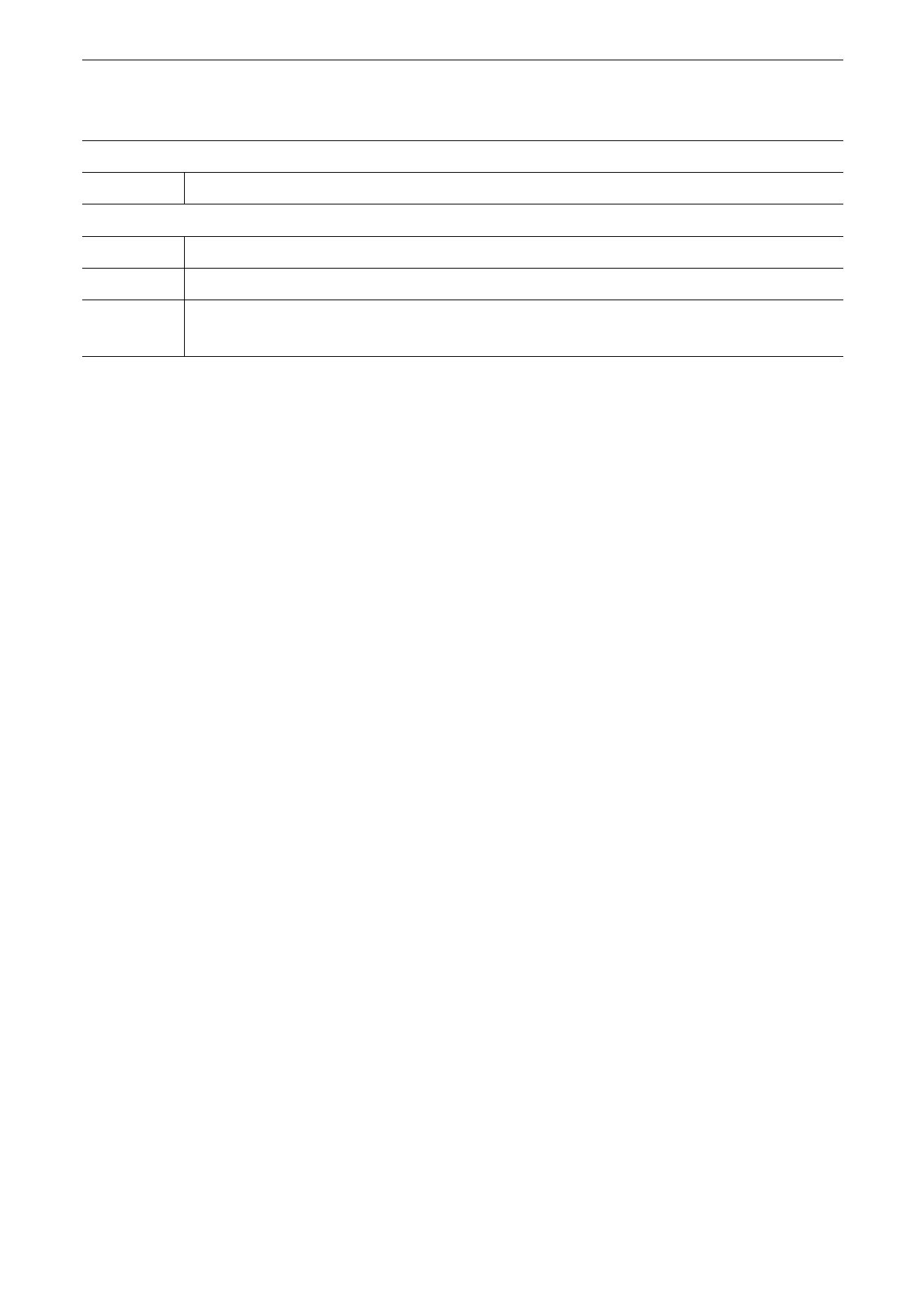

Número de pieza

componentes Descripción

Lista de partido

PEB20954 Datasheet PDF : 132 Pages

| |||

PEB 20954

PEF 20954

1

1.1

1.2

1.3

2

2.1

2.2

3

3.1

3.1.1

3.1.2

3.1.3

3.1.4

3.1.5

3.1.6

3.1.7

3.1.8

3.1.9

3.1.10

3.1.11

3.1.12

3.2

3.2.1

3.2.2

3.2.3

4

4.1

4.2

4.3

4.3.1

4.3.2

4.3.3

4.3.4

4.3.5

4.3.6

4.3.7

4.3.8

4.3.8.1

4.3.8.2

4.3.9

5

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

Key Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6

Logic Symbol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

Typical Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

Pin Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

Pin Definitions and Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

Functional Block Diagram and Description . . . . . . . . . . . . . . . . . . . . . . . . .24

Speech Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

Disabling Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

Adaptive Echo Estimation Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

PCM Input/Output Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

Subtractor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

Non Linear Processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

Microprocessor Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

Universal Control and Communication Interface . . . . . . . . . . . . . . . . . . .26

Watchdog Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

Clock Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

JTAG and RAM BIST . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

Description of Functional Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

Channelwise and Global A- and µ-Law Conversion . . . . . . . . . . . . . . . .27

Bypass and Disabling Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

UCC Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

Operational Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

Pin Connection Diagram for SIDEC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

Synchronization and Clock Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

Timing Patterns . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

Clock Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

PCM Signal Timing and Frame Alignment . . . . . . . . . . . . . . . . . . . . . . . .41

Timing of SYNCI and SYNCO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

Clock Timing within External VCO Capture Range . . . . . . . . . . . . . . . . .46

Serial Interface (Controlling and Monitoring) Timing . . . . . . . . . . . . . . . .47

UCC Interface Signal Timing and Frame Alignment . . . . . . . . . . . . . . . .49

Speech Highway Control Signals for CAS in T1 Systems . . . . . . . . . . . .53

Microprocessor Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

Intel Mode (IM0=’0’) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .56

Motorola Mode (IM0=’1’) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58

JTAG Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .64

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65

Preliminary Data Sheet

3

04.99