RTL8019AS Ver la hoja de datos (PDF) - Realtek Semiconductor

Número de pieza

componentes Descripción

Lista de partido

RTL8019AS

RTL8019AS Datasheet PDF : 50 Pages

| |||

SPECIFICATION

RTL8019AS

0

ACTIVEB This bit is the inverse of bit 0 in PnP Activate register (index 30H).

When RTL8019AS is deactivated, all BROM memory read and I/O accesses to the

Group1 registers except the HLTCLK register are ignored.

The HLTCLK register and PnP logic work the same as when RTL8019AS is active.

Note: The PnP logical device control register is the only way to activate

RTL8019AS. Therefore, the HLTCLK register is allowed to be written to prevent

RTL8019AS from dying when it is inactive in the clock-halted power-down mode.

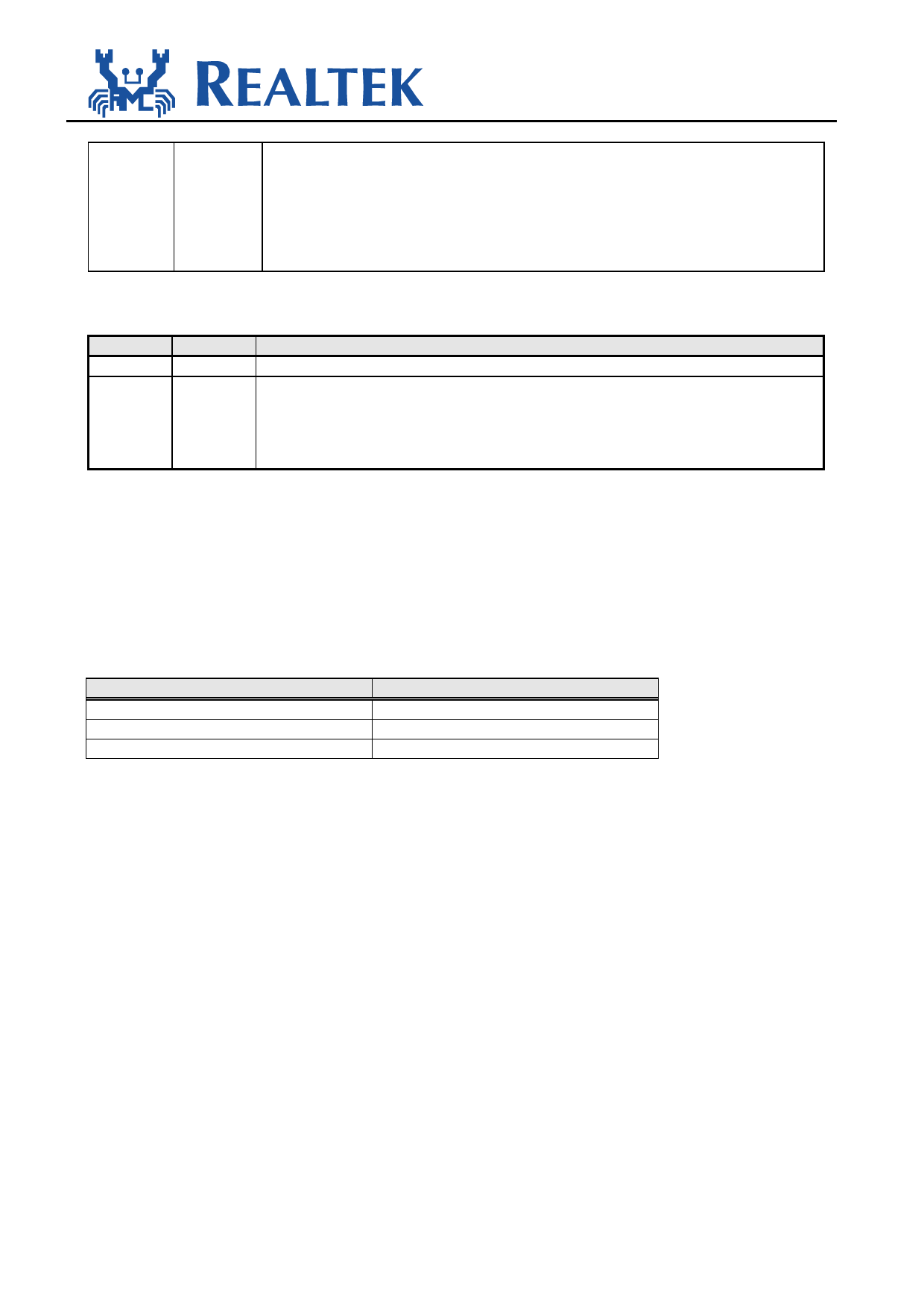

CONFIG4 RTL8019AS Configuration Register 4 (0DH; Type=R)

Bit

Symbol

Description

7-1

-

Reserved

0

IOMS When this bit is set, RTL8019AS uses SA15-SA0 to decode I/O address of NE2000

registers. When this bit is reset, RTL8019AS only decodes SA9-SA0 like the RTL8019

does. This mode is supported for applications which might require to fully decode I/O

address. This bit is read-only and comes from the CONFIG4 byte(Offset 03H) of

9346(refer to section 6.3).

CSNSAV: CSN Save Register (08H; Type=R)

This register is provided to backup the CSN assigned to the PnP CSN register.

HLTCLK: Halt Clock Register (09H; Type=W)

This is the only active one of Group1 registers when RTL8019AS is inactivated.

Writing to this register is invalid if RTL8019AS is not in power down mode. (i.e. If PWRDN bit

in CONFIG3 register is zero.)

The data written to this register determines the RTL8019AS's power down mode.

Data

52H (ASCII code of 'R')

48H (ASCII code of 'H')

Other values

Power Down Mode

Mode 1 - clock Running

Mode 2 - clock Halted

Ignored

INTR: Interrupt Register (0BH; Type=R)

This register reflects the ISA bus states of INT7-0 pins.

FMWP: Flash Memory Write Protect Register (0Ch, Type=W)

This register is write only. A write to this register is valid only when EEM0=EEM1=1.

Sequentially writing 2 bytes of data (57H then A8H) to this register enables the flash memory

write operation. Writing other data to this register will reset the write sequence and disable the

flash write. All flash memory write commands from host are ignored if the write operation is not

enabled.

8019AS.doc

22

2001-04-02