STLC60135 Ver la hoja de datos (PDF) - STMicroelectronics

Número de pieza

componentes Descripción

Lista de partido

STLC60135 Datasheet PDF : 7 Pages

| |||

TOSCA STLC60134/STLC60135

block drives, through the STLC60134’s integrated

VCXO controller, the NT crystal oscillator which

comes up in an excellent synchronisation (less

than 2ppm) between ATU-C and ATU-R.

FRAMING Functions

STLC60135 performs framing functions for ge-

neric and ATM TC sub layers.

ATM TC sub layer performs cell level functions: de-

lineation, idle cells or unassigned cells insertion/ex-

traction, payload scrambling, Header Error Correc-

tion (HEC) check and data frame generation.

In order to comply with T1.413 Issue 2 rules and

full interoperability with other manufacturers’ mo-

dems (providing they guarantee compliance with

either Issue 1 or Issue 2) framing features (such

as interleaving and fast mode) are implemented

with programmable parameters.

ATM frames can be bypassed in order to carry

non-ATM bit streams, which makes the chip set

very fit for applications using dedicated framing

such as Frame-relay, etc.

STLC60135 DTM modem main features:

Time-domain equalisation

Decimation, interpolation,

FFT and IFFT, with different length and sam-

pling rate at ATU-C and ATU-R side

Rotor and frequency-domain equalisation

Mapping/demapping

Trellis coding and decoding using Viterbi algo-

rithm

Error and noise monitoring on individual tones

Reed-Solomon encoding and decoding

(De) framing and (de) interleaving

Cell HEC generation/verification

Payload (de) scrambling

ATM cell insertion/extraction

Idle &/or Unassigned cell insertion/filtering

VPI/VCI filtering

UTOPIA interface (Level 1 or 2)

Microcontroller interface with 16-bit multi-

plexed address/data bus and big/little endian

format supported

JTAG test port

Single 3.3V supply, 1.0W

PQFP144 (28 x 28mm body, 0.65mm pitch)

ADSL Modem control software

The ADSL transceiver is based on a programma-

ble DMT modem (STLC60135) whose configura-

tion is loaded by an external controller.

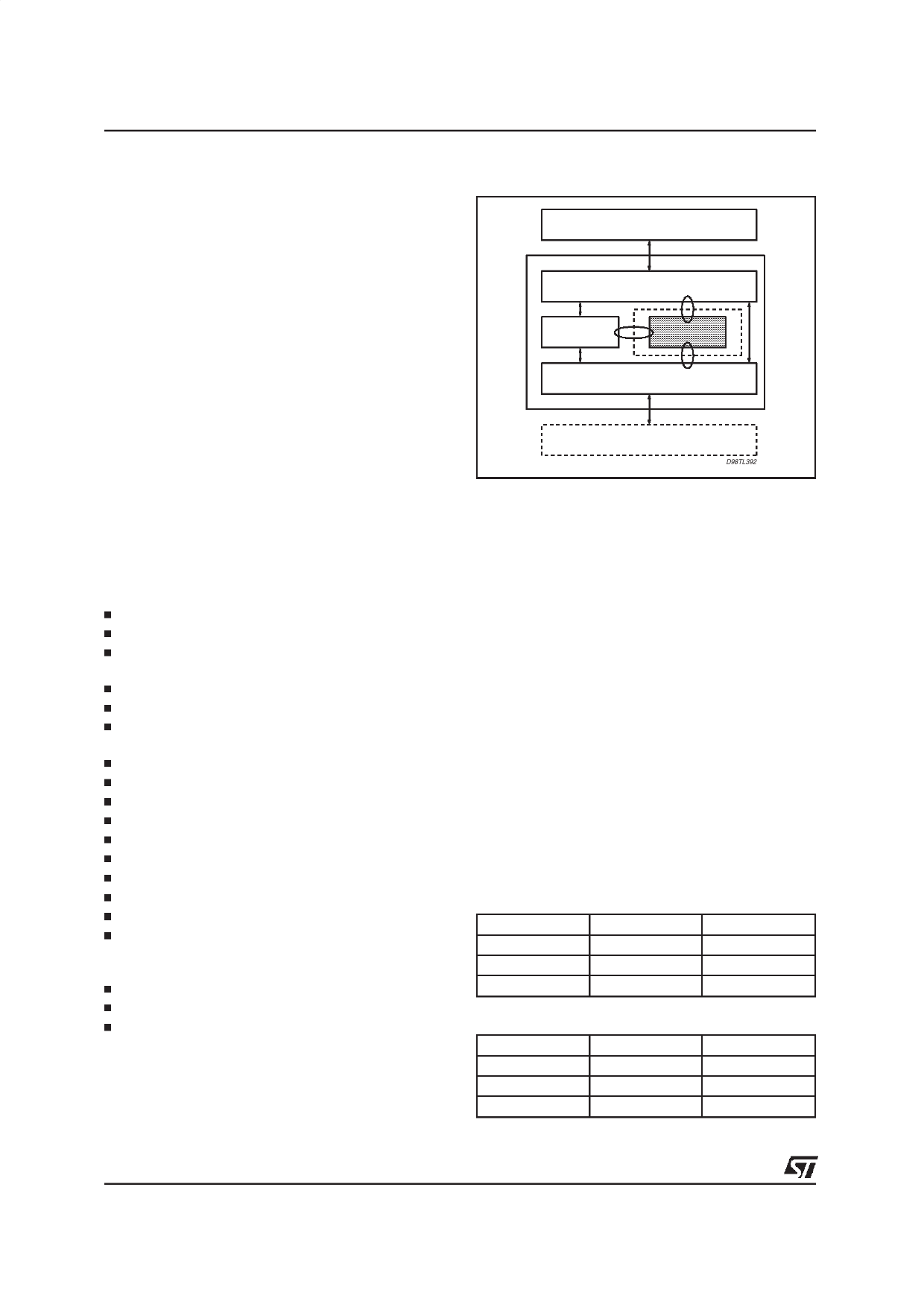

Figure 4. Software Architecture.

USER HIGH LEVEL SOFTWARE

ADSL MANAGEMENT APPLICATION SW

OS INTERFACE

MODEM SW

BOARD SUPPORT PACKAGE

ADSL HARDWARE

D98TL392

Additionally the control functions, STMicroelec-

tronics provides the DTM modem software. The

software is written in C++ language, and is de-

signed to be portable to any processor.

The driver has to be interfaced with a real time

OS kermel, it is compatible with any standard

product available on the market. The kernel man-

ages the tasks dedicated to modem software.

The modem 5W core comes with three additional

two software modules: a Board Support Package

(BSP) and two Application Program Interfaces

(API). BSP manages the hardware dependent

features (i.e. interrupts, peripheral mapping).

APIs interface to the higher level application soft-

ware and to the OS.

ADSL Loop performances

The hereafter tables show the performances that

a system, which houses TOSCA, can achieve for

ANSI and ETSI loops. The following results refer

to an end-to end ADSLequipment with no exter-

nal disturbance.

ANSI Loop (26awg)

Length

9Kft

12Kft

15Kft

Downstream

7.47 E +0.6

3.69 E +0.6

1.56 E +0.6

Upstream

1.05 E +06

9.37 E +05

7.25 E +05

ETSI Loop (Loop 2, noise model A)

Length

2Km

4Km

5Km

Downstream

8.00 E +0.6

4.07 E +0.6

1.70 E +0.6

Upstream

8.32 E +05

6.72 E +05

4.72 E +05

4/7