TDA9178 Ver la hoja de datos (PDF) - Philips Electronics

Número de pieza

componentes Descripción

Lista de partido

TDA9178

TDA9178 Datasheet PDF : 36 Pages

| |||

Philips Semiconductors

YUV one chip picture improvement based on luminance

vector-, colour vector- and spectral processor

Preliminary specification

TDA9178

Successive approximation ADC

Pins ADEXT1, ADEXT2 and ADEXT3 are connected to a

6-bit successive approximation ADC via a multiplexer.

The multiplexer toggles between the inputs with each field.

At each field flyback, a conversion is started for two of the

three inputs and the result is stored in the corresponding

bus register ADEXT1, ADEXT2 or ADEXT3. The input pin

ADEXT1 is updated every field, while input fields

ADEXT2 and ADEXT3 are updated once in two

consecutive fields (see Figs 7, 8, 9 and 10). Once in

32 fields the ADEXT2 input is not updated, because then

the noise measurement is updated.

In this way, any slow varying analog signal can be given

access to the I2C-bus. If a register access conflict occurs,

the data of that register is made invalid by setting the flag

bit DV (Data Valid) to zero.

Smart noise control

With the help of the internal noise detector and a

user-preferred noise algorithm, the user can make a fully

automatic I2C-bus feature reduction, briefly called ‘Smart

Noise Control’.

Demonstration mode

By the I2C-bus bit DEM all the picture improvement

features can be demonstrated in one picture. By setting

bit DEM to logic 1, all the features selected by the user are

active for 5 s in 1fH mode (in 2fH mode: 2.5 s), and for

another 5 s in 1fH mode (in 2fH mode: 2.5 s) all features

selected are turned off (then the TDA9178 is ‘transparent’

to the incoming signal).

Internal window

To determine the histogram levels and the black offset the

TDA9178 performs several measurements. An internally

defined window serves to exclude parts in the scene like

‘subtitling’ or ‘logos’. The internal window can be regarded

as a weighting function which has a value of one within a

square near the centre of the screen and which gradually

decreases to zero towards the edges.

When bit WLB (Window Letter Box) is made logic 1, the

height of the window is reduced by a factor of 2⁄3.

This prevents the contribution of the black bars above and

below a 16 : 9 scene to the measurements.

I2C-bus

The I2C-bus is always in standby mode and responds on a

properly addressed command. Bit PDD (Power-Down

Detected) in the status register is set each time an

interruption of the power supply occurs and is reset only by

reading the status register. A 3-bit identification code can

also be read from the status register, which code can be

used to automatically configure the application by

software.

The input control registers can be written sequentially by

the I2C-bus by the embedded automatic subaddress

increment feature or by addressing them directly.

The output control functions cannot be addressed

separately. Reading out the output control functions

always starts at subaddress 00H and all subsequent

words are read out by the automatic subaddress

increment procedure.

The bits in the I2C-bus are preset to logic 0 at power-on

except for bits AMS and VG5: therefore the TDA9178 is in

1.0 V luminance signal range and the variable gamma is

set to 20H (gamma correction 0%).

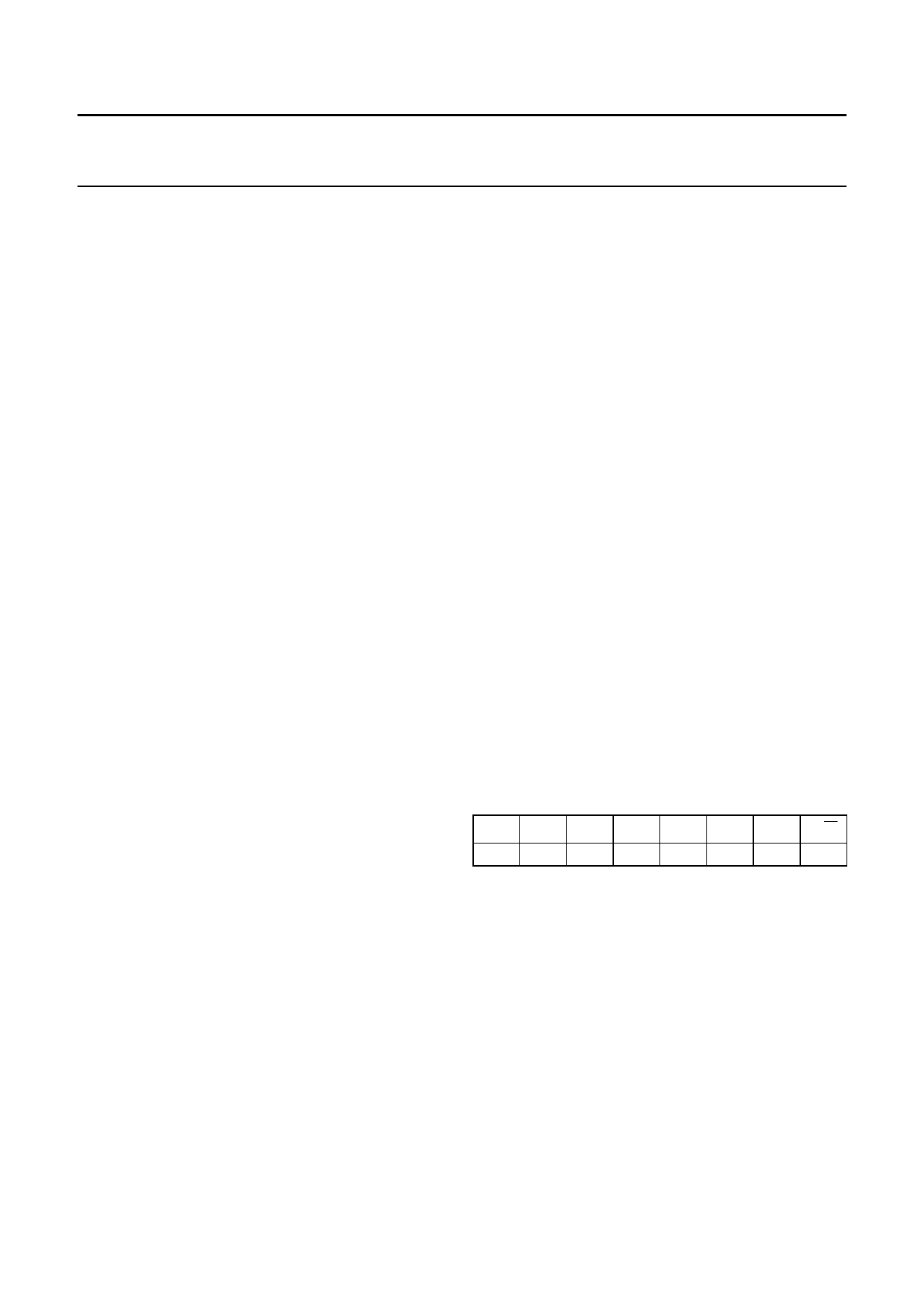

I2C-BUS SPECIFICATION

The slave address of the IC is given in Table “Slave

address”. If pin ADR of the TDA9178 is connected to

ground, the I2C-bus address is 40H; if pin ADR is

connected to pin DECDIG, the I2C-bus address is E0H.

The circuit operates on clock frequencies up to 400 kHz.

Slave address

A6 A5 A4 A3 A2 A1 A0 R/W

ADR 1 ADR 0

0

0

0

X

Auto-increment mode is available for subaddresses.

1999 Sep 24

10