T7502 Ver la hoja de datos (PDF) - Agere -> LSI Corporation

Número de pieza

componentes Descripción

Lista de partido

T7502 Datasheet PDF : 16 Pages

| |||

Data Sheet

February 1998

T7502 Dual PCM Codec with Filters

Pin Information (continued)

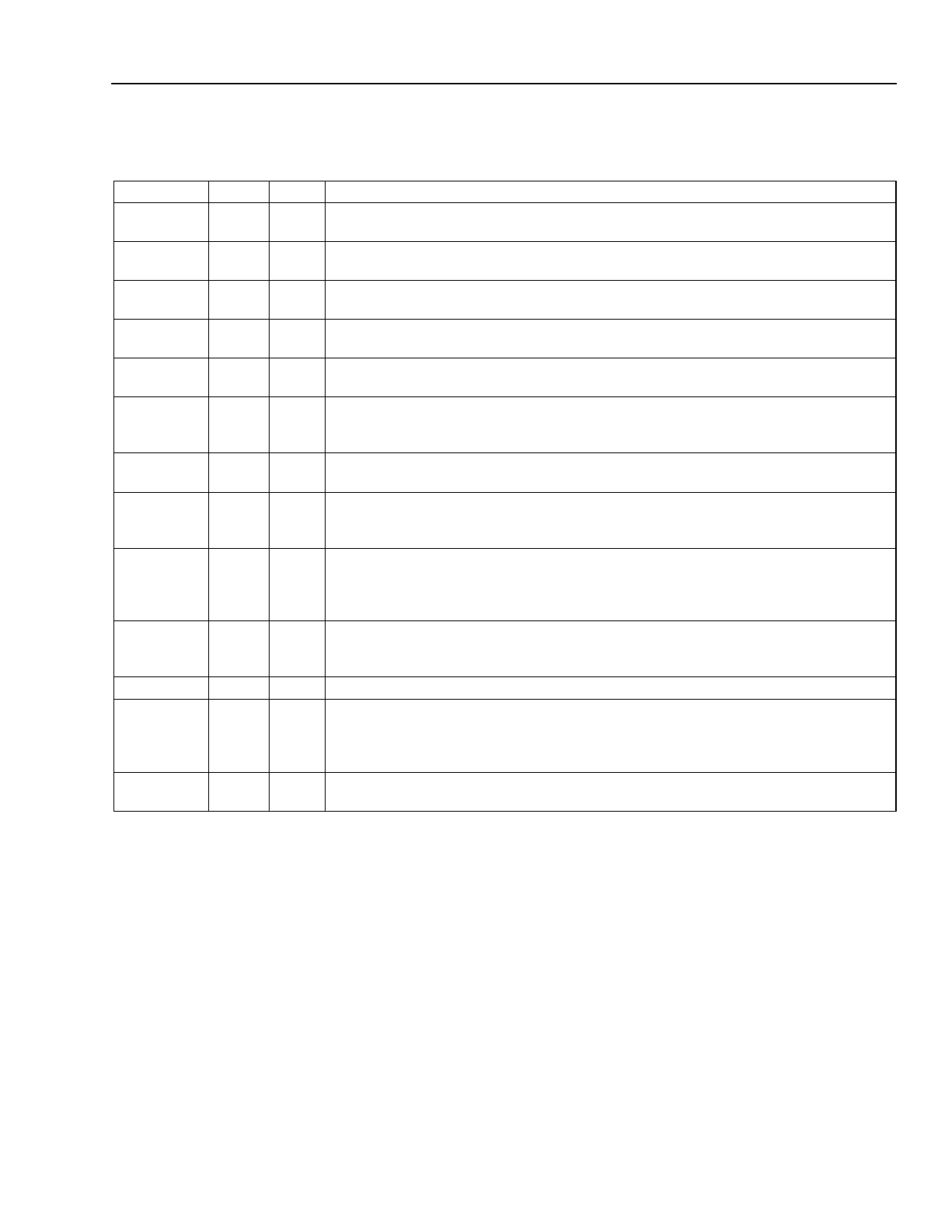

Table 1. Pin Descriptions

Symbol Pin Type

Name/Function

VFXIN1

17

VFXIN0

4

I Voice Frequency Transmitter Negative Input. Analog inverting input to the

uncommitted operational amplifier at the transmit filter input.

VFXIP1

16

VFXIP0

5

I Voice Frequency Transmitter Positive Input. Analog noninverting input to the

uncommitted operational amplifier at the transmit filter input.

GSX1

GSX0

15

O Gain Set for Transmitter. Output of the transmit uncommitted operational amplifi-

6

er. The pin is the input to the transmit differential filters.

VFROP1

20

VFROP0

1

O Voice Frequency Receiver Positive Output. This pin can drive ≥300 Ω loads.

VFRON1

19

VFRON0

2

O Voice Frequency Receiver Negative Output. This pin can drive ≥300 Ω loads.

VDD

8

— +5 V Power Supply. This pin should be bypassed to analog ground with at least

0.1 µF of capacitance as close to the device as possible. VDD serves both analog

and digital internal circuits.

GNDA1

18

— Analog Grounds. Both ground pins must be connected on the circuit board. AGND

GNDA0

3

serves both analog and digital internal circuits.

DR

12

I Receive PCM Data Input. The data on this pin is shifted into the device on the fall-

ing edges of MCLK. Sixteen consecutive bits of data (8 bits for channel 0, and

8 bits for channel 1) are entered after the FS pulse has been detected.

DX

11

O Transmit PCM Data Output. This pin remains in the high-impedance state except

during active transmit time slots. Sixteen consecutive bits of data (8 bits for

channel 0 and 8 bits for channel 1) are shifted out on the rising edge of MCLK. Data

is shifted out on the rising edge of MCLK.

MCLK

9

I Master Clock Input. The frequency must be 2.048 MHz or 4.096 MHz. This clock

serves as the bit clock for all PCM data transfer. A 40% to 60% duty cycle is re-

quired.

GNDD

10

— Digital Ground. Ground connection for the digital circuitry.

FS

13

Id* Frame Sync. This signal is an edge trigger and must be high for a minimum of one

MCLK cycle. This signal must be derived from MCLK. If FS is low for 500 µs while

MCLK remains active, then the device fully powers down. An internal pull-down de-

vice is included on FS.

VCM0

VCM1

7

O Voltage Common Mode. 2.4 Vdc.

14

* Id indicates a pull-down device is included on this lead.

Lucent Technologies Inc.

3