AX88140A Ver la hoja de datos (PDF) - Unspecified

Número de pieza

componentes Descripción

Lista de partido

AX88140A Datasheet PDF : 46 Pages

| |||

AX88140A

PRELIMINARY

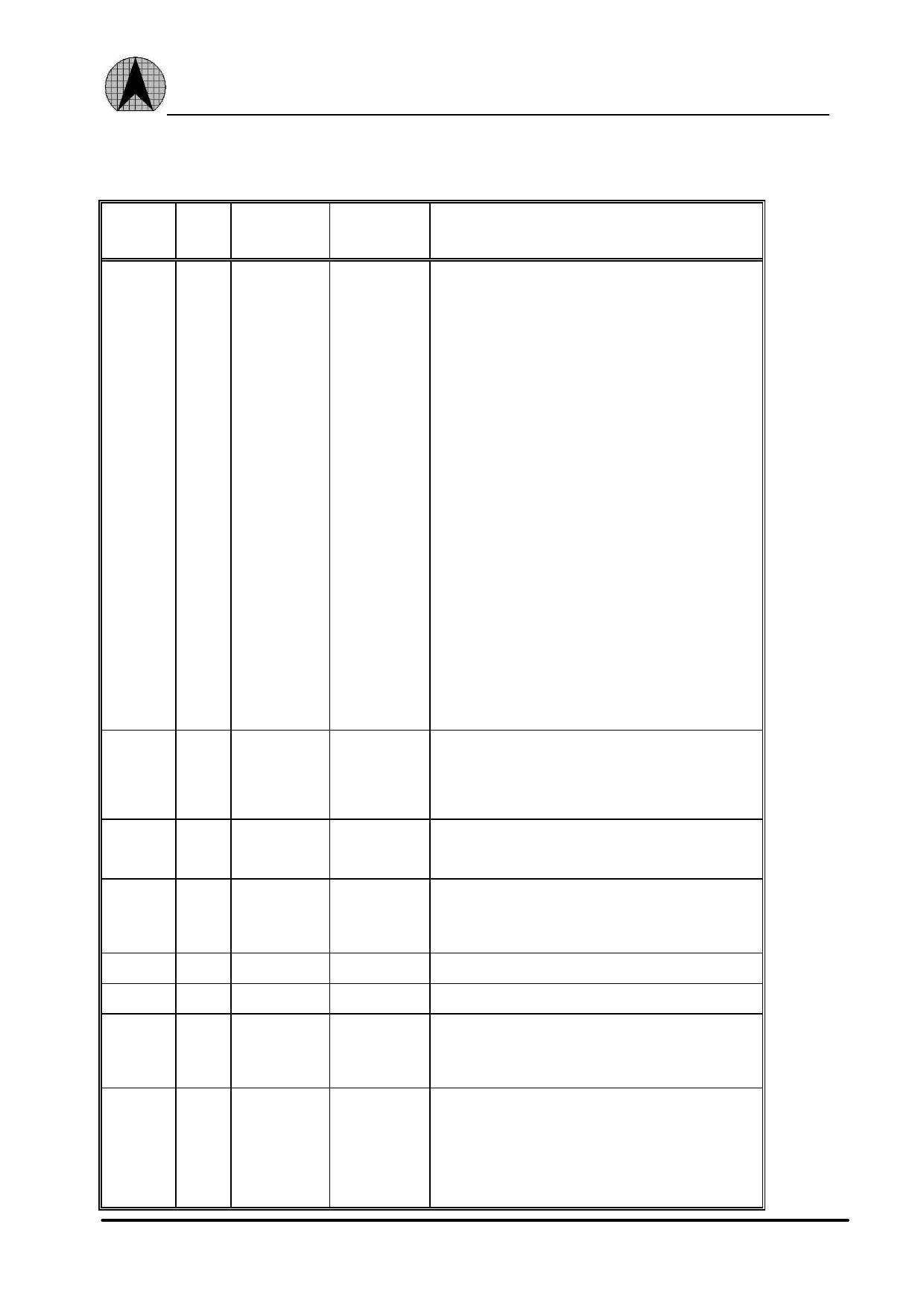

2.2 PCI interface group

SIGNAL

AD<31>

AD<30>

AD<29>

AD<28>

AD<27>

AD<26>

AD<25>

AD<24>

AD<23>

AD<22>

AD<21>

AD<20>

AD<19>

AD<18>

AD<17>

AD<16>

AD<15>

AD<14>

AD<13>

AD<12>

AD<11>

AD<10>

AD<9>

AD<8>

AD<7>

AD<6>

AD<5>

AD<4>

AD<3>

AD<2>

AD<1>

AD<0>

CBE#<3>

CBE#<2>

CBE#<1>

CBE#<0>

DEVSEL#

FRAME#

GNT#

IDSEL

INT#

IRDY#

TYPE

PIN

PIN

DESCRIPTION

NUMBER NUMBER

FOR 160 PIN FOR 144 PIN

I/O

12,

13,

15,

16,

18,

19,

21,

22,

26,

27,

28,

29,

31,

32,

36,

37,

56,

57,

58,

60,

61,

63,

64,

66,

68,

69,

71,

72,

74,

75,

77,

78

I/O

23,

44,

54,

67

I/O

48

I/O

45

I

9

I

24

O/D

3

I/O

46

10,

Address and data bits are multiplexed on the same pins. During the

11,

address phase, the AD<31:0> contain a physical address (32 bits).

13,

During, data phases, AD<31:0> contain 32 bits of data.

14,

The AX88140A supports both read and write bursts (in master

16,

operation only). Little and big endian byte ordering can be used.

17,

19,

20,

24,

25,

26,

27,

29,

30,

34,

35,

50,

51,

52,

54,

55,

57,

58,

60,

62,

63,

65,

66,

68,

69,

71,

72

21,

BUS COMMAND and BYTE ENABLE Are multiplexed on the

38,

same PCI pins. During the address phase of the transaction,

48,

CBE#<3:0> Provide the BUS COMMAND. During the data phase,

61

CBE#<3:0> Provide the BYTE ENABLE. The BYTE ENABLE

determines which byte lines carry valid data., CBE#<0> Applies to

byte 0, and CBE#<3> Applies to byte 3.

42

Device select Is asserted by the target of the current bus access.

When the AX88140A is the master of the current bus access, the

target assert DEVSEL# confirming the access. It is driven by

AX88140A When AX88140A is selected as a slave.

39

The FRAME# Signal is driven by the AX88140A To indicate the

beginning and duration of an access. FRAME# Asserts to indicate

the beginning of a bus transaction. While FRAME# is asserted,

data transfers continue. When FRAME# deasserts the next data

phase is the final data phase transaction.

7

BUS GRANT Indicates to the AX88140A That access to the bus is

granted.

22

Initialization devise select asserts To indicate that the host is

issuing a configuration cycle to the AX88140A.

1

Interrupt request asserts When one of the appropriate bits of reg5

sets and causes an interrupt, provided that the corresponding mask

bit in reg7 is not asserted. interrupt request deasserts by writing a 1

into the appropriate crs5 bit.

This pin must be pulled up by an external resistor.

40

Initiator ready Indicates the bus master ability to complete the

current data phase of the transaction.

A data phase is completed on any rising edge of the clock When

both IRDY# and target ready TRDY# are asserted. Wait cycles are

inserted until both IRDY# and TRDY# are asserted together.

When the AX88140A is the bus master, IRDY# is asserted during

write operations to indicate that valid data is present on the

AD<31:0>. During read operations, the AX88140A asserts

12

ASIX ELECTRONICS CORPORATION