IMIC9835CY Ver la hoja de datos (PDF) - Cypress Semiconductor

Número de pieza

componentes Descripción

Lista de partido

IMIC9835CY

IMIC9835CY Datasheet PDF : 18 Pages

| |||

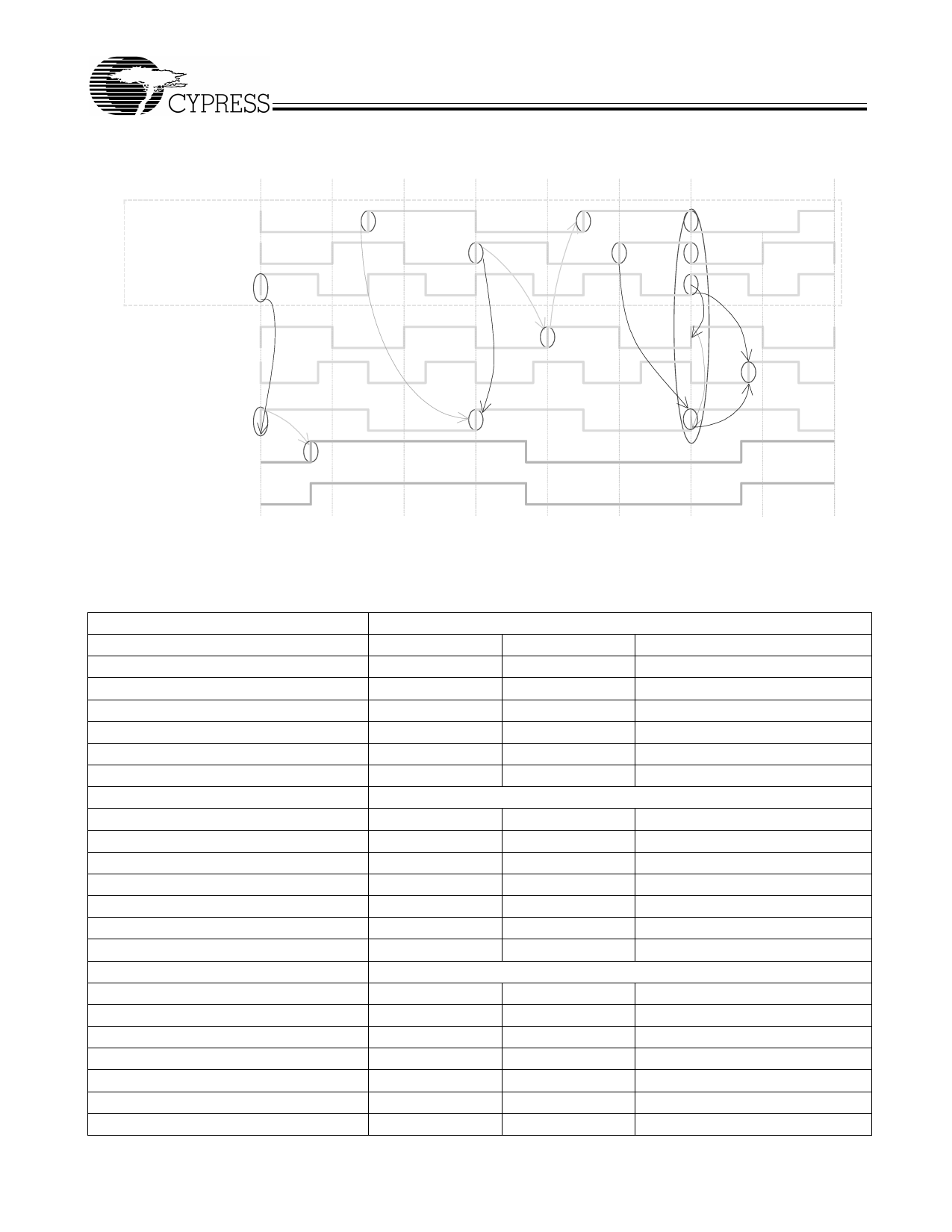

Clock Phase

0ns

10ns

CPU CLOCK 66MHz

CPU CLOCK 100MHz

CPU CLOCK 133MHz

DCLK/SDRAM CLOCK 100MHz

0ns

DCLK/SDRAM CLOCK 133MHz

3V66 CLOCK 66MHz 1.5ns~3.5

PCI CLOCK 33MHz

IOAPIC CLOCK 33MHz

7.5ns

C9835

20ns

30ns

40ns

2.5ns

5ns

5ns

0ns

Sync

0ns

3.75ns

0nS

3.75ns

Figure 4.

Table 4. Group Timing Relationships and Tolerances

CPU to SDRAM/DCLK

CPU to 3V66

SDRAM/DCLK to 3V66

3V66 to PCI

PCI to IOAPIC

48M (0,1)

CPU to SDRAM/DCLK

CPU to 3V66

SDRAM/DCLK to 3V66

3V66 to PCI

PCI to IOAPIC

48M (0,1)

CPU to SDRAM/DCLK

CPU to 3V66

SDRAM/DCLK to 3V66

3V66 to PCI

PCI to IOAPIC

48M (0,1)

Offset (ns)

2.5

7.5

0

1.5–3.5

0

Async

Offset (ns)

5

5

0

1.5–3.5

0

Async

Offset(ns)

0

0

0

1.5–3.5

0

Async

CPU = 66.6 MHz, SDRAM = 100 MHz

Tolerance (ps)

Conditions

500

500

180 degrees phase shift

500

When rising edges line up

500

3V66 leads

1000

N/A

CPU = 100 MHz, SDRAM = 100 MHz

Tolerance (ps)

Conditions

500

180 degrees phase shift

500

CPU leads

500

When rising edges line up

500

3V66 leads

1000

N/A

CPU = 133.3 MHz, SDRAM = 100 MHz

Tolerance(ps)

Conditions

500

When rising edges line up

500

500

When rising edges line up

500

3V66 leads

1000

N/A

Document #: 38-07303 Rev. **

Page 6 of 18