BD9483F Ver la hoja de datos (PDF) - ROHM Semiconductor

Número de pieza

componentes Descripción

Lista de partido

BD9483F Datasheet PDF : 32 Pages

| |||

BD9483F,FV

Datasheet

Status

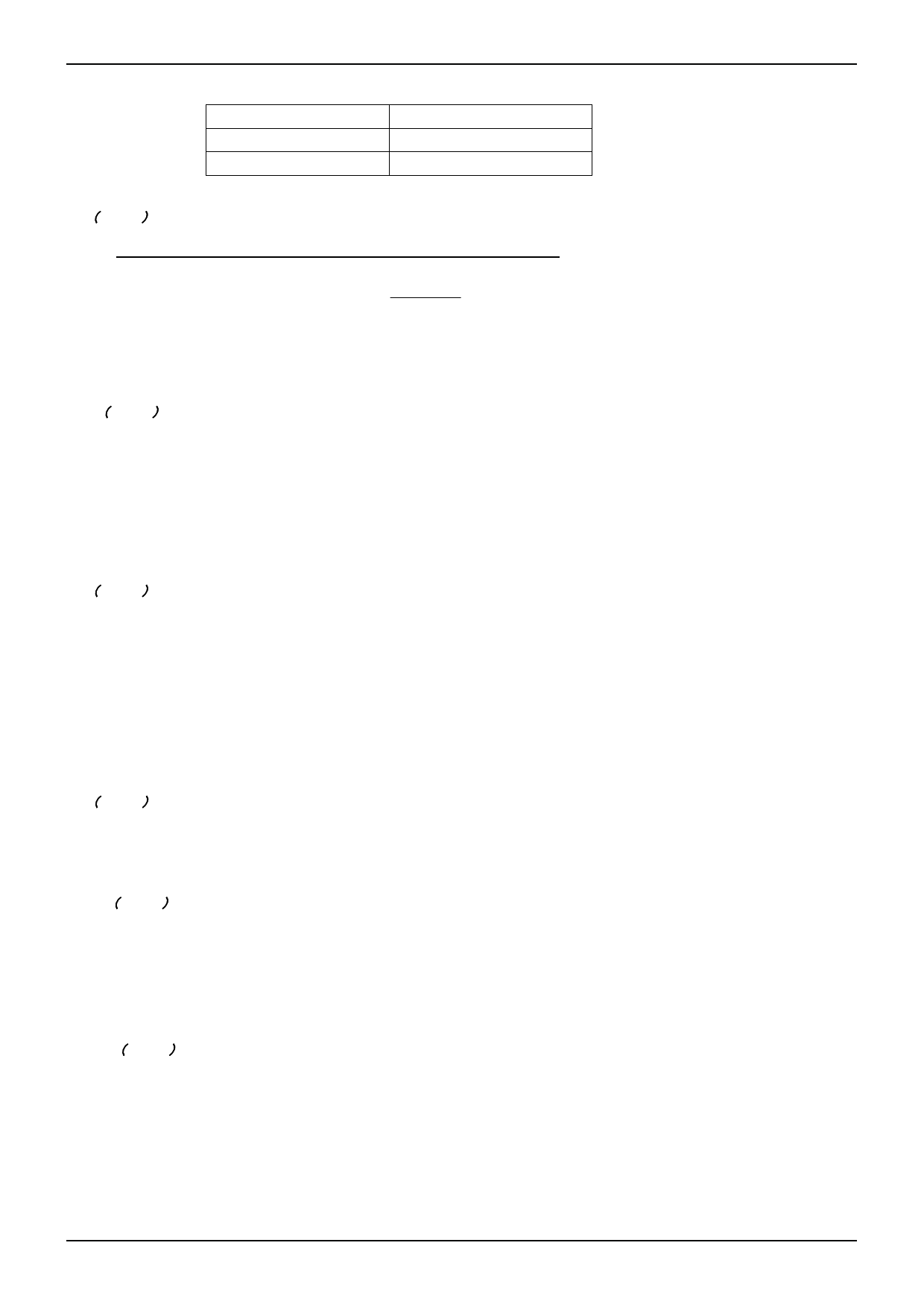

Normal

Abnormal

FAILB output

OPEN

GND Level

RT (13 PIN)

DC/DC switching frequency setting pin. RT set the oscillation frequency inside IC.

○The relationship between the frequency and RT resistance value (ideal)

R RT

15000

fSW [kHz]

[k Ω ]

The oscillation setting range from 50kHz to 800kHz.

The setting examples is separately described in the section ” ●3.4.4 how to set DCDC oscillation frequency”

OVP (14 PIN)

The OVP terminal is the input for over-voltage protection. As OVP is more than 3.0V, the over-voltage protection (OVP)

will work. At the moment of these detections, the BD9483F,FV stops the switching of the output GATE and starts to count

up the abnormal interval, but IC doesn't reach latch off state instantaneously until the detection continues up to 4 counts

of GATE terminals. (Please refer to the time chart 3.7.4)

As the latch off by OVP, both channels stop. (GATE1=GATE2=L, DIMOUT1=DIMOUT2=L)

The OVP pin is high impedance, because the internal resistance to a certain bias is not connected.

So, the bias by the external components is required, even if OVP function is not used, because the open connection of

this pin is not fixed the potential.

The setting examples is separately described in the section ”●3.4.6 how to set OVP”

SS (15 PIN)

The pin which sets soft start interval of DC/DC converter. It performs the constant current charge of 3.0 μA to external

capacitance Css(0.001μF to 4.7μF). The switching duty of GATE output will be limited during 0V to 4.0V of the SS

voltage.

So the equality of the soft start interval can be expressed as following

Tss = 1.33*106*Css

Css: the external capacitance of the SS pin.

Regarding of the logic of SS=L

(SS=L) = (PWM1orPWM2 have not asserted H since ResetB=L->H) or (latch off state)

where ResetB = (STB=H) and (VCCUVLO=H) and (REG90UVLO=H)

Please refer to the time chart 3.7.3 on soft start behavior

CP (16 PIN)

Timer pin for counting the abnormal state of the FBMAX protection. If the abnormal state is detected, The CP pin start

charging by 3μA to the external capacitance. As the CP voltage reaches to 3.0V, IC will be latched off. In latch off both

channels will be stopped (GATE1=GATE2=L, DIMOUT1=DIMOUT2=L).

Please refer to the section “●3.4.7 how to set the interval until latch off (CP pin)” for more detail.

UVLO (17 PIN)

Under voltage lock out pin for the input voltage of the power stage. More than 3.0V(typ.), IC starts the boost operation

and stops lower than 2.8V(typ.).

The UVLO pin is high impedance, because the internal resistance to a certain bias is not connected.

So, the bias by the external components is required, even if UVLO function is not used, because the open connection of

this pin is not fixed the potential.

As the latch off by UVLO, both channels stop. (GATE1=GATE2=L, DIMOUT1=DIMOUT2=L)

The setting examples is separately described in the section ”●3.4.5 how to set UVLO”

REG90 (24 PIN)

This is the 9.0V (typ.) output pin that is used for the power supply of DIMOUT, GATE. Available current is 15mA (min.).

When VCC<11V , REG90 output voltage decreases because of the saturation.

www.rohm.com

© 2012 ROHM Co., Ltd. All rights reserved.

TSZ22111・15・001

11/29

TSZ02201-0F1F0C100100-1-2

28.Nov.2013 Rev.003