RTL8101 Ver la hoja de datos (PDF) - Realtek Semiconductor

Número de pieza

componentes Descripción

Lista de partido

RTL8101

RTL8101 Datasheet PDF : 68 Pages

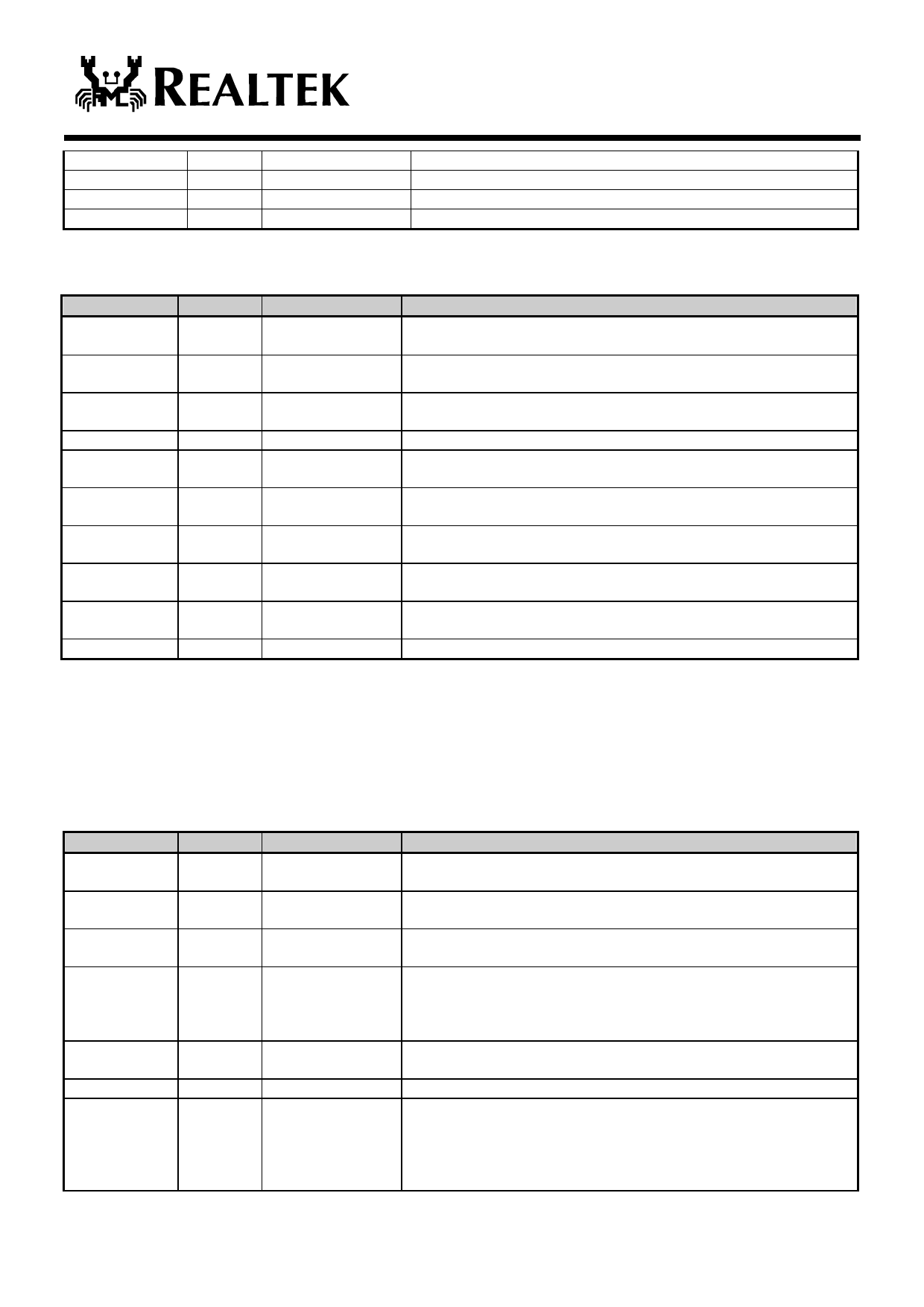

| |||

00D3h

R/W

00D4h-00D7h

-

00D8h

R/W

00D9h-00FFh

-

LSBCRC7

-

Config5

-

RTL8101L

LSB of the mask byte of wakeup frame7 within offset 12 to 75

Reserved.

Configuration register 5

Reserved.

5.1 Receive Status Register in Rx packet header

Bit

R/W

Symbol

Description

15

R

MAR

Multicast Address Received: This bit set to 1 indicates that a multicast

packet is received.

14

R

PAM

Physical Address Matched: This bit set to 1 indicates that the destination

address of this packet matches the value written in ID registers.

13

R

BAR

Broadcast Address Received: This bit set to 1 indicates that a broadcast

packet is received. BAR, MAR bit will not be set simultaneously.

12-6

-

-

Reserved

5

R

ISE

Invalid Symbol Error: (100BASE-TX only) This bit set to 1 indicates

that an invalid symbol was encountered during the reception of this packet.

4

R

RUNT

Runt Packet Received: This bit set to 1 indicates that the received packet

length is smaller than 64 bytes ( i.e. media header + data + CRC < 64 bytes )

3

R

LONG

Long Packet: This bit set to 1 indicates that the size of the received

packet exceeds 4k bytes.

2

R

CRC

CRC Error: When set, indicates that a CRC error occurred on the

received packet.

1

R

FAE

Frame Alignment Error: When set, indicates that a frame alignment

error occurred on this received packet.

0

R

ROK

Receive OK: When set, indicates that a good packet is received.

5.2 Transmit Status Register (TSD0-3)

(Offset 0010h-001Fh, R/W)

The read-only bits (CRS, TABT, OWC, CDH, NCC3-0, TOK, TUN) will be cleared by the RTL8101L when the Transmit Byte

Count (bits 12-0) in the corresponding Tx descriptor is written. It is not affected when software writes to these bits. These registers

are only permitted to write by double-word access. After a software reset, all bits except OWN bit are reset to “0”.

Bit

31

30

29

28

27-24

23-22

21-16

R/W

R

R

R

R

R

-

R/W

Symbol

CRS

TABT

OWC

CDH

NCC3-0

-

ERTXTH5-0

Description

Carrier Sense Lost: This bit is set to 1 when the carrier is lost during

transmission of a packet.

Transmit Abort: This bit is set to 1 if the transmission of a packet was

aborted. This bit is read only, writing to this bit is not affected.

Out of Window Collision: This bit is set to 1 if the RTL8101L encountered

an "out of window" collision during the transmission of a packet.

CD Heart Beat: The NIC watches for a collision signal (ie, CD

Heartbeat signal) during the first 6.4us of the interframe gap following a

transmission. This bit is set if the transceiver fails to send this signal.

This bit is cleared in the 100 Mbps mode.

Number of Collision Count: Indicates the number of collisions

encountered during the transmission of a packet.

Reserved

Early Tx Threshold: Specifies the threshold level in the Tx FIFO to

begin the transmission. When the byte count of the data in the Tx FIFO

reaches this level, (or the FIFO contains at least one complete packet) the

RTL8101L will transmit this packet.

000000 = 8 bytes

2003-05-28

13

Rev.1.3