88E3016 Ver la hoja de datos (PDF) - Marvell Semiconductor

Número de pieza

componentes Descripción

Lista de partido

88E3016 Datasheet PDF : 106 Pages

| |||

88E3016

Integrated 10/100 Fast Ethernet Transceiver

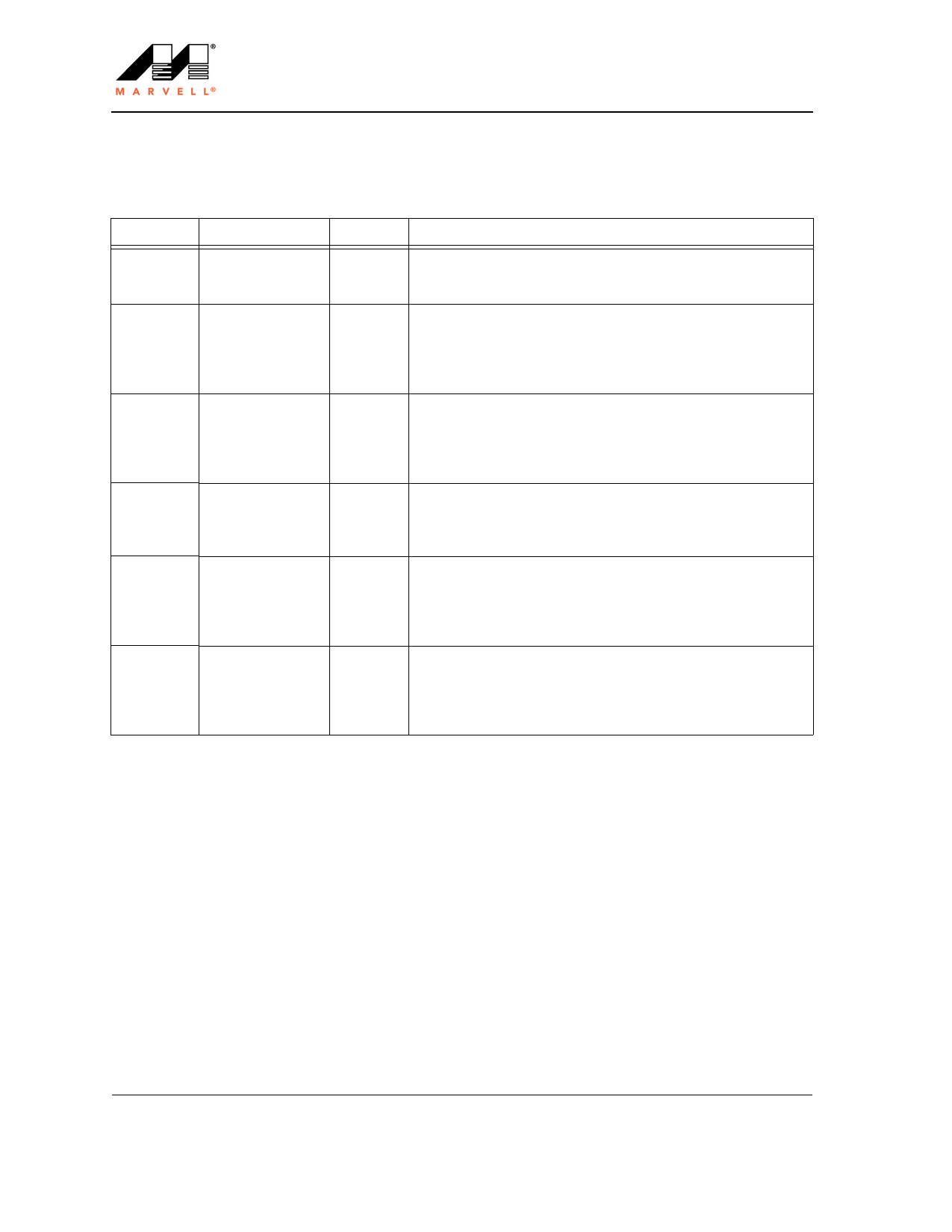

Table 1: RGMII Interface

88E3016

60

Pin Name

TX_CLK/TXC

Ty p e

I

63

TX_CTRL/TX_CTL I

62

TXD[3]/TD[3]

I

61

TXD[2]/TD[2]

59

TXD[1]/TD[1]

58

TXD[0]/TD[0]

53

RX_CLK/RXC

O

49

RX_CTRL/

O

RX_CTL

55

RXD[3]/RD[3]

O

54

RXD[2]/RD[2]

51

RXD[1]/RD[1]

50

RXD[0]/RD[0]

Description

RGMII Transmit Clock provides a 25 MHz or 2.5 MHz reference

clock with ± 50 ppm tolerance depending on speed. In RGMII

mode, TX_CLK is used as TXC.

RGMII Transmit Control. TX_EN is presented on the rising edge of

TX_CLK. In RGMII mode, TX_CTRL is used as TX_CTL.

A logical derivative of TX_EN and TX_ER is presented on the fall-

ing edge of TX_CLK.

RGMII Transmit Data. In RGMII mode, TXD[3:0] are used as

TD[3:0].

The transmit data nibble is presented on TXD[3:0] on the rising

edge of TX_CLK.

RGMII Receive Clock provides a 25 MHz or 2.5 MHz reference

clock with ± 50 ppm tolerance derived from the received data

stream depending on speed. In RGMII mode, RX_CLK is used as

RXC.

RGMII Receive Control. RX_DV is presented on the rising edge of

RX_CLK. In RGMII mode, RX_CTRL is used as RX_CTL.

A logical derivative of RX_DV and RX_ER is presented on the fall-

ing edge of RX_CLK.

RGMII Receive Data. In RGMII mode, RXD[3:0] are used as

RD[3:0].

The receive data nibble is presented on RXD[3:0] on the rising

edge of RX_CLK.

Doc. No. MV-S103164-00, Rev. A

Page 10

Document Classification: Proprietary Information

Copyright © 2008 Marvell

January 4, 2008, Advance