IDT72511 Ver la hoja de datos (PDF) - Integrated Device Technology

Número de pieza

componentes Descripción

Lista de partido

IDT72511 Datasheet PDF : 28 Pages

| |||

IDT72511/IDT72521

BIDIRECTIONAL FIRST-IN FIRST-OUT MEMORY

MILITARY AND COMMERCIAL TEMPERATURE RANGES

Port B Interface

Port B has reread/rewrite and DMA functions. Port B can

be configured to interface to either Intel-style (RB, WB) or

Motorola-style (DSB, R/WB) devices in Configuration Register

5 (see Table 10). Port B can also be configured to talk to a

processor or a peripheral device through Configuration Reg-

ister 5. In processor interface mode, the Port B interface

controls are inputs. In peripheral interface mode, the Port B

interface controls are outputs. After a hardware reset or a

software Reset All command, Port B defaults to an Intel-style

processor interface; the controls are inputs.

DMA Control Interface

The BiFIFO has DMA control to simplify data transfers with

peripherals. For the BiFIFO DMA controls (REQ, ACK and

CLK) to operate, the BiFIFO must be in peripheral interface

mode (Configuration Register 5, Table 10).

DMA timing is controlled by the external clock input, CLK.

An internal clock is derived from this CLK signal to generate

the RB, WB, DSB and R/WB output signals. The internal clock

also determines the timing between REQ assertion and ACK

assertion. Bit 9 of Configuration Register 5 determines whether

the internal clock is the same as CLK or whether the internal

clock is CLK divided by 2.

Bit 8 of Configuration Register 5 set whether RB, WB and

DSB are asserted for 1 or 2 internal clocks. Bits 6 and 7 of

Configuration Register 5 set the number of clocks between

REQ assertion and ACK assertion. The clocks between REQ

assertion and ACK assertion can be 2, 3, 4 or 5.

Bits 4 and 5 of Configuration Register 5 set the polarity of

the REQ and ACK pins respectively.

A DMA transfer command sets the Port B read/write

direction (see Table 5). The timing diagram for DMA transfers

is shown in Figure 17. The basic DMA transfer starts with REQ

assertion. After 2 to 5 internal clocks, ACK is asserted by the

BiFIFO. ACK will not be asserted if a read is attempted on an

empty A→B FIFO or if a write is attempted on a full B→A FIFO.

If the BiFIFO is in Motorola-style interface mode, R/WB is set

at the same time that ACK is asserted. One internal clock later,

DSB is asserted. If the BiFIFO is in Intel-style interface mode,

either RB or WB is asserted one internal clock after ACK

assertion. These read/write controls stay asserted for 1 or 2

internal clocks, then ACK, DSB, RB and WB are made inactive.

This completes the transfer of one 9-bit word.

On the next rising edge of CLK, REQ is sampled. If REQ

is still asserted, another DMA transfer starts with the assertion

of ACK. Data transfers will continue as long as REQ is

asserted.

Intelligent Reread/Rewrite

Intelligent reread/rewrite is a method the BiFIFO uses to

help assure data integrity. Port B of the BiFIFO has two extra

pointers, the Reread Pointer and the Rewrite Pointer.The

Reread Pointer is associated with the A->B FIFO Read

Pointer, while the Rewrite Pointer is associated with the B->A

FIFO Write Pointer. The Reread Pointer holds the start ad-

dress of a data block in the A->B FIFO RAM, and the Read

Pointer is the current address of the same FIFO RAM array.

By loading the Read Pointer with the value held in the Reread

Pointer (RER asserted), reads will start over at the beginning

of the data block. In order to mark the beginning of a data

block, the Reread Pointer should be loaded with the Read

Pointer value (LDRER asserted) before the first read is

performed on this data block. Figure 6 shows a Reread

operation.

Similarly, the Rewrite Pointer holds the start address of a

data block in the B->A FIFO RAM, while the Write Pointer is

the current address within the RAM array. The operation of the

REW and LDREW is identical to the RER and LDRER dis-

cussed above. Figure 7 shows a Rewrite operation.

For the reread data protection, Bit 2 of Configuration

Register 5 can be set to 1 to prevent the data block from being

overwritten. In this way, the assertion of A->B full flag will occur

when the write pointer meets the reread pointer instead of the

read pointer as in the normal definition. For the rewrite data

protection, Bit 3 of Configuration Register 5 can be set to 1 to

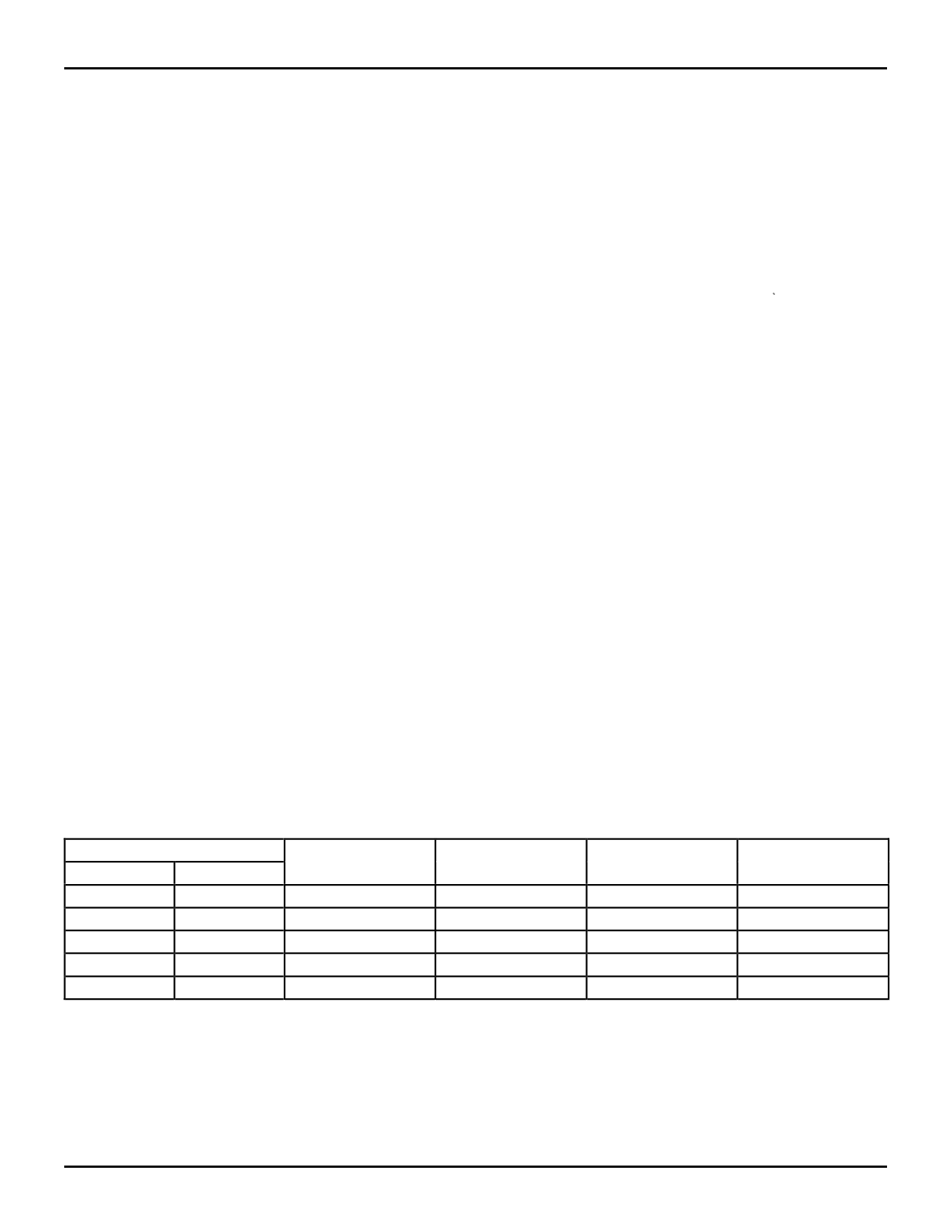

INTERNAL FLAG TRUTH TABLE

Number of Words in FIFO

From

To

Empty Flag

Almost-Empty Flag Almost-Full Flag

Full Flag

0

0

Asserted

Asserted

Not Asserted

Not Asserted

1

n

Not Asserted

Asserted

Not Asserted

Not Asserted

n+1

D – (m + 1)

Not Asserted

Not Asserted

Not Asserted

Not Asserted

D–m

D–1

Not Asserted

Not Asserted

Asserted

Not Asserted

D

D

Not Asserted

Not Asserted

Asserted

Asserted

NOTE:

2668 tbl 15

1. BiFIFO flags must be assigned to external flag pins to be observed. D = FIFO depth (IDT72511 = 512, IDT72521 = 1024), n = Almost-Empty flag

offset, m = Almost-Full flag offset.

Table 11. Internal Flag Truth Table

5.32

12