7480 Ver la hoja de datos (PDF) - Renesas Electronics

Número de pieza

componentes Descripción

Lista de partido

7480 Datasheet PDF : 98 Pages

| |||

PRELIMINARY NSootimcee: pTahriasmisentroict alimfinitsalasrpeescuifbicjeactitotno. change.

MITSUBISHI MICROCOMPUTERS

7480/7481 GROUP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

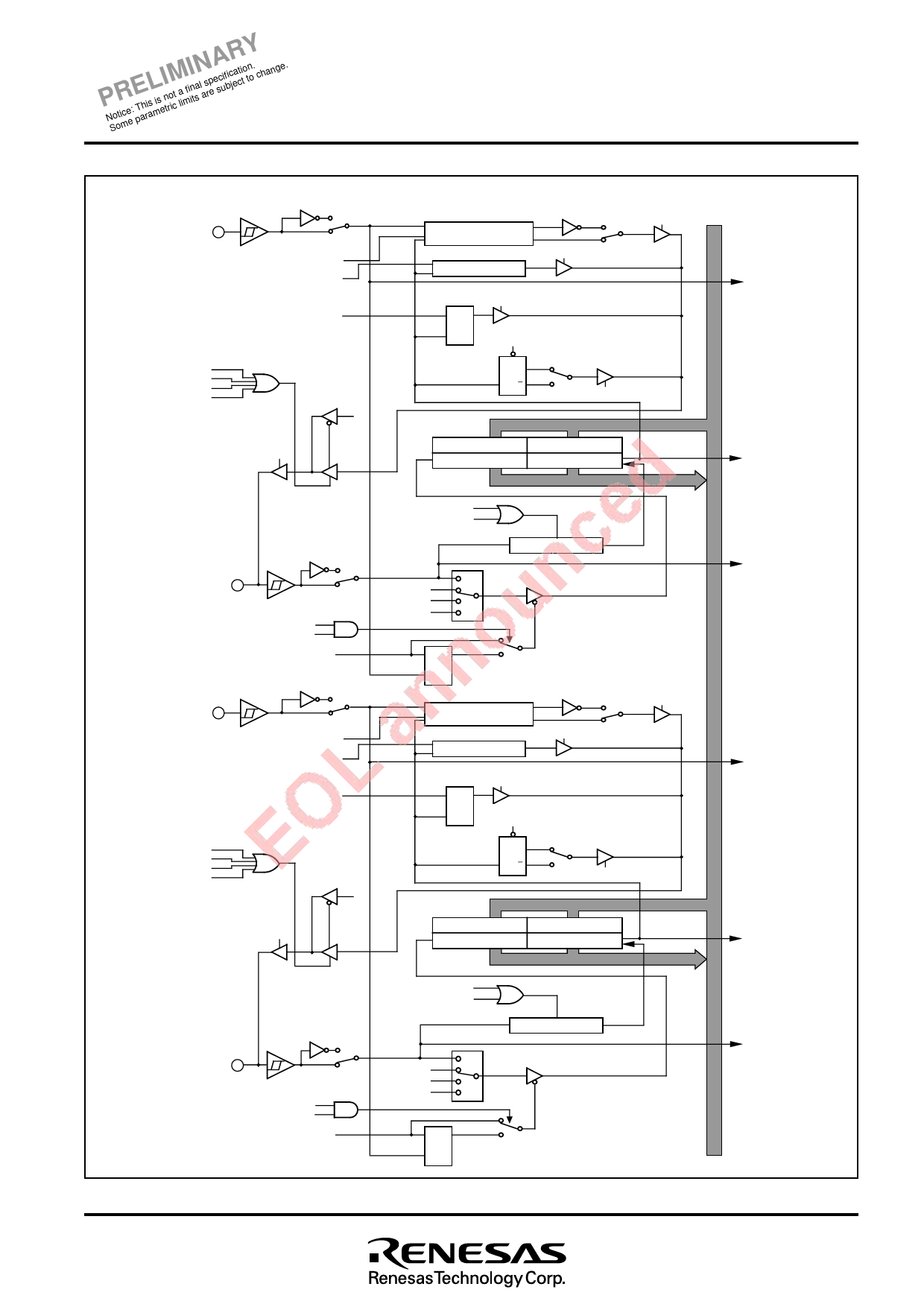

P30/INT0

“1”

“0”

INT0 edge selection bit

Programmable one-shot

output mode

PWM mode

Output level latch

“001”

“100”

“101”

“110”

Timer X

operating mode bits

P40 direction

register

P40

latch

Programmable one-shot

output circuit

PWM generating circuit

CNTR0 edge

selection bit

“1”

PWM mode “0”

Programmable waveform

generation mode

Programmable

one-shot

output mode Data bus

INT0 interrupt

request

DQ

T

Pulse output

mode

S

Q

CNTR0 edge

selection bit

“0”

TQ

“1” Pulse output mode

Timer X (low-order) latch Timer X (high-order) latch

Timer X (low-order)

Timer X (high-order)

Timer X

interrupt request

Pulse width measurement mode

Pulse cycle measurement mode

P40/CNTR0

CNTR0 edge

selection bit

“1”

“0”

Programmable waveform generation mode

Timer X trigger selection bit

Timer X stop control bit

P31/INT1

“1”

“0”

INT1 edge selection bit

Programmable one-shot

output mode

PWM mode

Output level latch

“001”

“100”

“101”

“110”

Timer Y

operating mode bits

P41 direction

register

P41

latch

Edge detecting circuit

f(XIN)/2

f(XIN)/8

f(XIN)/16

Timer X count source

selection bit

“0”

DQ

“1”

T

Programmable one-shot

output circuit

PWM generating circuit

CNTR1 edge

selection bit

“1”

PWM mode “0”

Programmable

one-shot

output mode

Programmable waveform

generation mode

DQ

T

Pulse output

mode

S

Q

CNTR1 edge

selection bit

“0”

TQ

“1” Pulse output mode

Timer Y (low-order) latch Timer Y (high-order) latch

Timer Y (low-order)

Timer Y (high-order)

CNTR0 interrupt

request

INT1 interrupt

request

Timer Y

interrupt request

P41/CNTR1

CNTR1 edge

selection bit

“1”

“0”

Programmable waveform generation mode

Timer Y trigger selection bit

Timer Y stop control bit

Fig. 17 Block diagram of timer X and timer Y

Pulse width measurement mode

Pulse cycle measurement mode

Edge detecting circuit

f(XIN)/2

f(XIN)/8

f(XIN)/16

DQ

T

Timer Y count source

selection bit

“0”

“1”

CNTR1 interrupt

request

24