LC86E7248 Ver la hoja de datos (PDF) - SANYO -> Panasonic

Número de pieza

componentes Descripción

Lista de partido

LC86E7248 Datasheet PDF : 19 Pages

| |||

LC86E7248

Pin name

Port A

(S0/PA0 –

S7/PA7)

Port B

(S8/PB0 –

S15/PB7)

Port C

(S16/PC0 –

S23/PC7)

I/O

Function description

I/O • Segment output terminal for LCD display -

• Can be used as a general input/output

port

I/O • Segment output terminal for LCD display -

• Can be used as a general input/output

port

I/O • Segment output terminal for LCD display -

• Can be used as a general input/output

port

Option

Port D

I/O • Segment output terminal for LCD display -

(S24/PD0 –

• Can be used as a general input/output

S31/PD7)

port

Port E

I/O • Segment output terminal for LCD display -

(S32/PE0 –

• Can be used as a general input/output

S39/PE7)

port

Port F

I/O • Segment output terminal for LCD display -

(S40/PF0 –

• Can be used as a general input/output

S47/PF7)

port

Port L

I/O • Common output terminal for LCD display -

(COM0/PL0

• Can be used as a general input port

–

COM3/PL3)

V1/PL4 –

I • Bias power terminal for LCD drive

-

V3/PL6

• Can be used as a general input port

RES

I Reset pin

-

XT1/ P74

I • Input pin for 32.768kHz crystal

-

oscillation

In case of non use, connect to VDD.

• Other function

A general input port P74

XT2/P75

O • Output pin for 32.768kHz crystal

-

oscillation

In case of non use, should be left

unconnected

(I) • Other function

A general input port P75

CF1

I Input pin for ceramic resonator

-

oscillation

CF2

O Output pin for ceramic resonator

-

oscillation

* All of port options can be specified in a bit unit except the pull-up resistor of port 0.

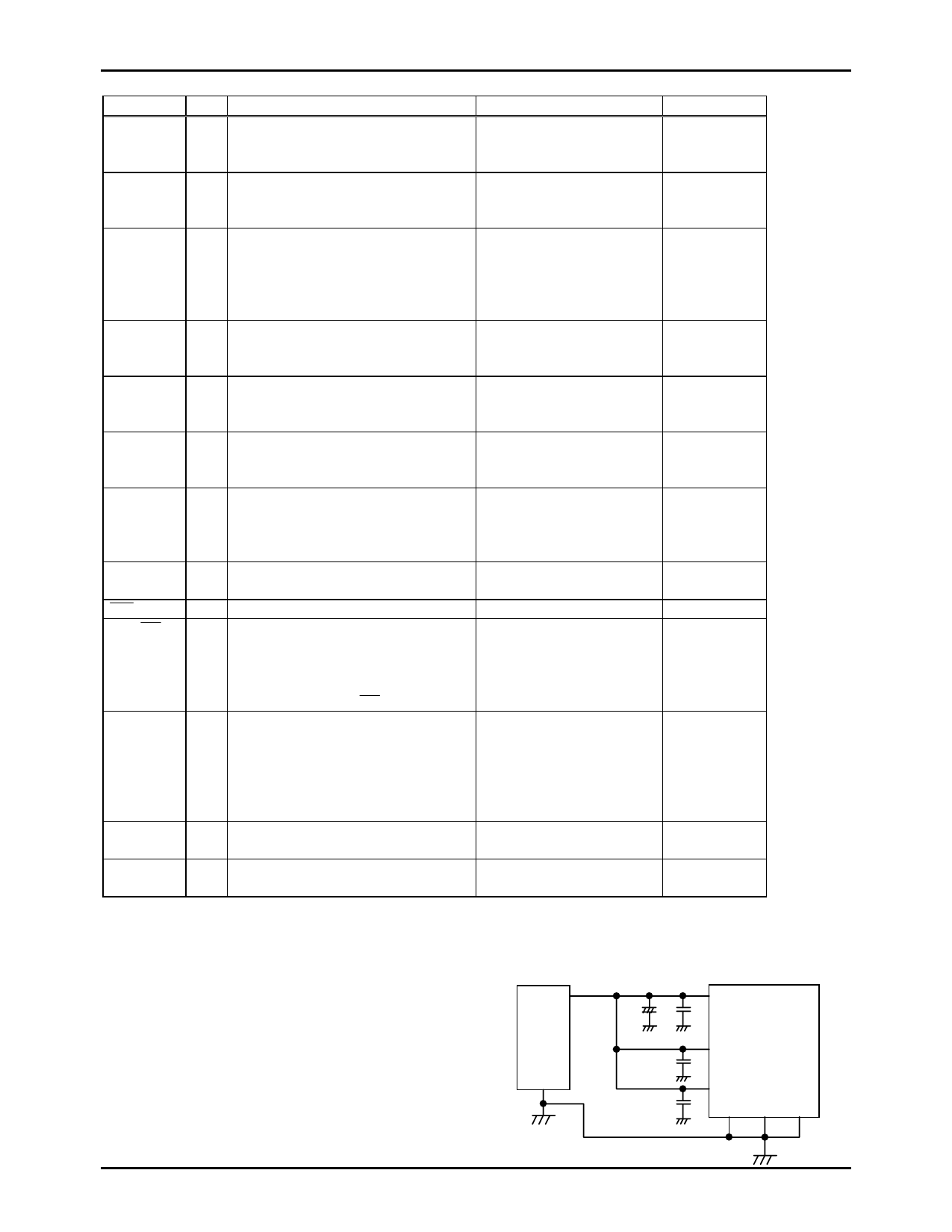

[Notes] • The VDD1, VDD2 and VDD3 terminals must be shorted electrically each other.

• The VSS1, VSS2 and VSS3 terminals must be shorted electrically each other.

*1 Connect like the following figure to reduce noise into a VDD terminals.

*2 Memory select input for data security

*3 Output enable input

*4 Chip enable input

*5 TA ! PROM control signal input

Power

Supply

PROM mode

Address input

A0 to A7

Address input

A8 to A13

PROM control

signal input

• TA (*5)

Address input

• A14, A15

-

-

-

-

-

-

-

-

-

-

LSI

VDD1

VDD2

VDD3

VSS1 VSS2 VSS3

No.6749-8/19