CAM35C44 Ver la hoja de datos (PDF) - SMSC -> Microchip

Número de pieza

componentes Descripción

Lista de partido

CAM35C44 Datasheet PDF : 50 Pages

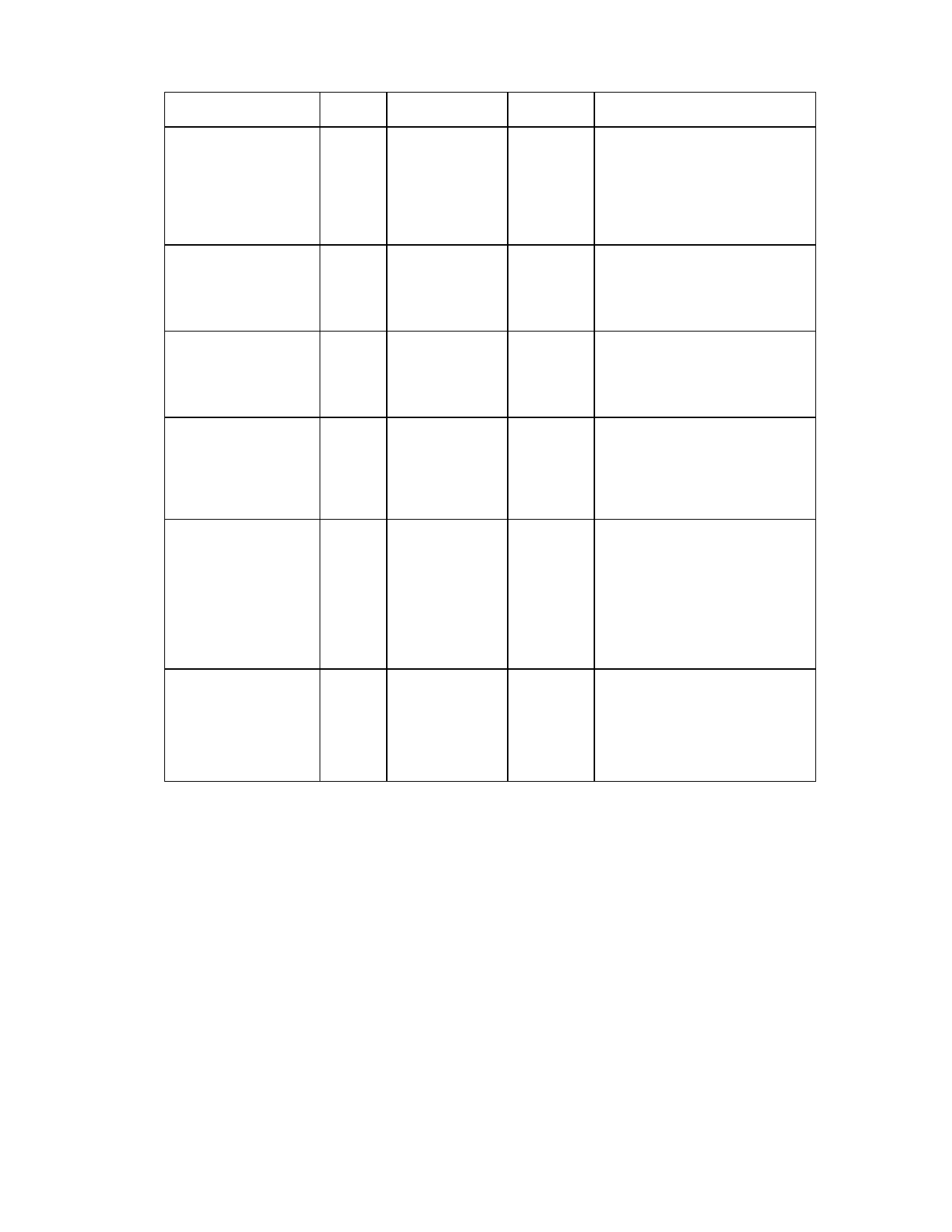

| |||

NAME

Address Enable

TOTAL

PINS

SYMBOL

1 AEN

ISA I/O Channel Ready

1

IOCHRDY

Multiplex Mode

Address Strobe

No Wait State

1 ASTRB

1 nNOWS

ISA Reset Drive

1 RESET_DRV

IRQ

1 IRQ

BUFFER

TYPE

I

OD12

I

OD12

IS

OD12

DESCRIPTION

The active high Address Enable

pin indicates DMA operations on

the host data bus. AEN must be

inactive to access the CAM35C44

registers and active during DMA

operations regardless of the

selected host interface type.

IOCHRDY is pulled low to extend

ISA I/O read/write commands.

Only SCE-driven functions in the

IrCC 2.0 can be enabled to use

IOCHRDY.

ASTRB is used to internally latch

I/O addresses during read/write

cycles when a multiplexed

address/data host interface type is

selected (TABLE 3).

nNOWS can be enabled to be

activated by IrCC 2.0 SCE-driven

functions to indicate that an

access cycle shorter than the

standard ISA I/O cycle can be

executed.

The RESET_DRV pin is active

high and is used to reset the

CAM35C44 as described in the

appropriate sections in this

document. The configuration

registers are not affected by this

pin except where noted (TABLE

13). The RESET_DRV pin must

be valid for 500ns minimum.

The IRQ pin is forced active when

an interrupt is asserted. IRQ goes

inactive as soon as the source of

the interrupt has been cleared.

The active IRQ pin-state is

determined by the IRQ_LEV bit in

CR00 (see page 22).

7