CAM35C44 Ver la hoja de datos (PDF) - SMSC -> Microchip

Número de pieza

componentes Descripción

Lista de partido

CAM35C44 Datasheet PDF : 50 Pages

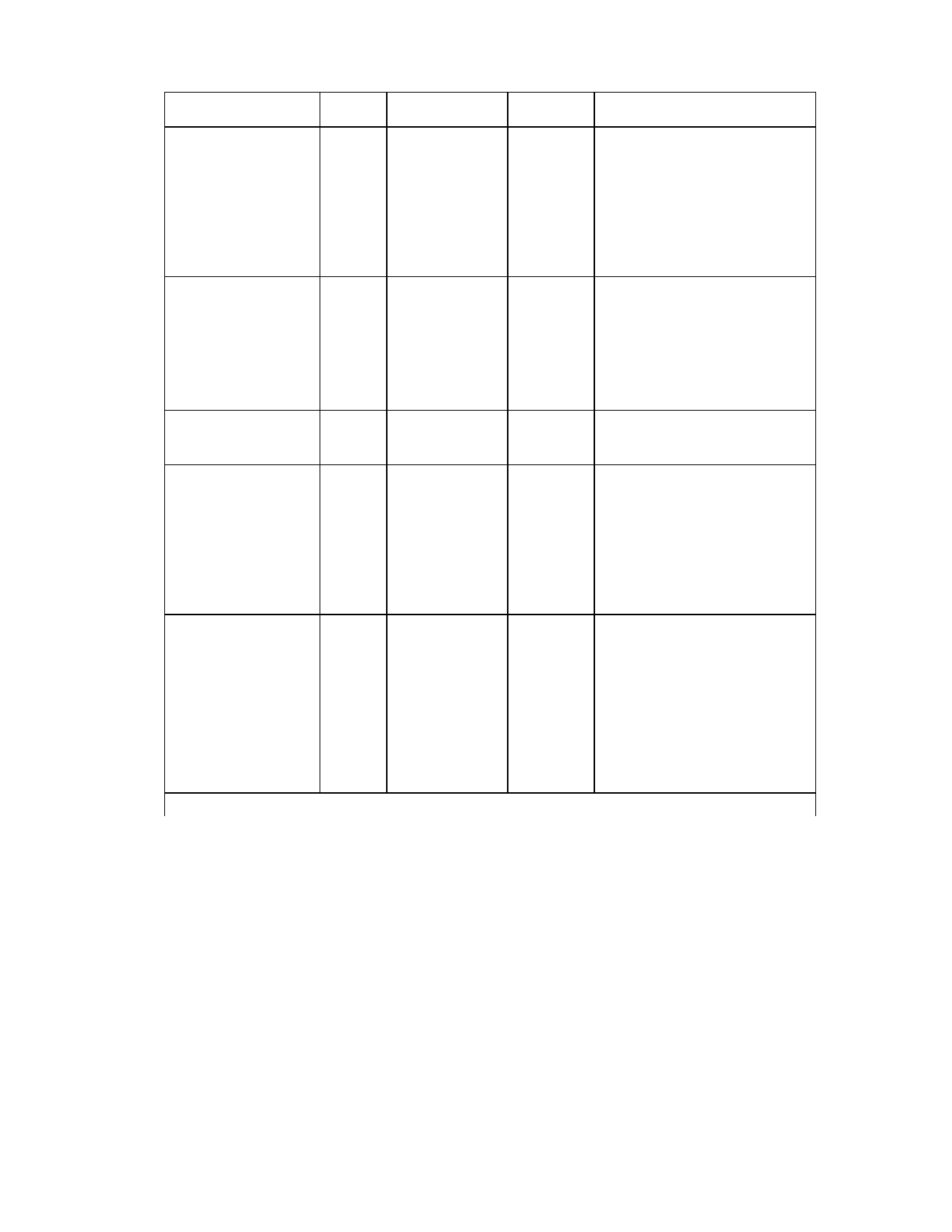

| |||

NAME

DMA Request

TOTAL

PINS

SYMBOL

1 DRQ

DMA Acknowledge

1 DACK

Terminal Count

ISA I/O Read/

Non-ISA Read/Write

Control

1 TC

1 nIOR/RnW

ISA I/O Write/

Non-ISA R/W Data

Strobe

1 nIOW/DSTRB

BUFFER

TYPE

O12

I

I

I

I

DESCRIPTION

The DRQ pin is forced active by

the CAM35C44 when byte

transfers to the host using DMA

are required. DRQ goes inactive

when the transfer has been

completed. The active DRQ pin-

state is determined by the

DRQ_LEV bit in CR01 (see page

22).

The DACK pin is forced active by

the host DMA controller to

acknowledge CAM35C44 transfer

requests. DACK goes inactive

following the transfer command.

The active DACK pin-state is

determined by the DAC_LEV bit in

CR01 (see page 23).

TC indicates that a DMA transfer

is complete. TC is only acknow-

ledged when DACK is active.

The active low nIOR input is

issued by the host to execute I/O

read commands when an ISA

read/write-styled host interface

type is selected (TABLE 3). The

RnW input is used to determine

the I/O command type when a

non-ISA read/write-styled host

interface type is selected.

The active low nIOW input is

issued by the host to execute I/O

write commands when an ISA

read/write-styled host interface

type is selected (TABLE 3). The

DSTRB input is used to execute

the I/O command when a non-ISA

read/write-styled host interface

type is selected (FIGURE 5).

MISCELLANEOUS (12)

8