CDB6420 Ver la hoja de datos (PDF) - Cirrus Logic

Número de pieza

componentes Descripción

Lista de partido

CDB6420 Datasheet PDF : 52 Pages

| |||

CS6420

placed between these two pins and loaded with

22 pF capacitors will allow the on-chip oscillator to

provide this system clock. Alternatively, the CLKI

pin may be driven by a CMOS level clock signal.

The clock may vary from 20.480 MHz by up to

10%, however, this will change the sampling rate

of the converters and echo canceller, which will af-

fect the bandwidth of the analog signals and the du-

ration of echo that the echo canceller can

accommodate. CLKO is not connected when CLKI

is driven by the CMOS signal.

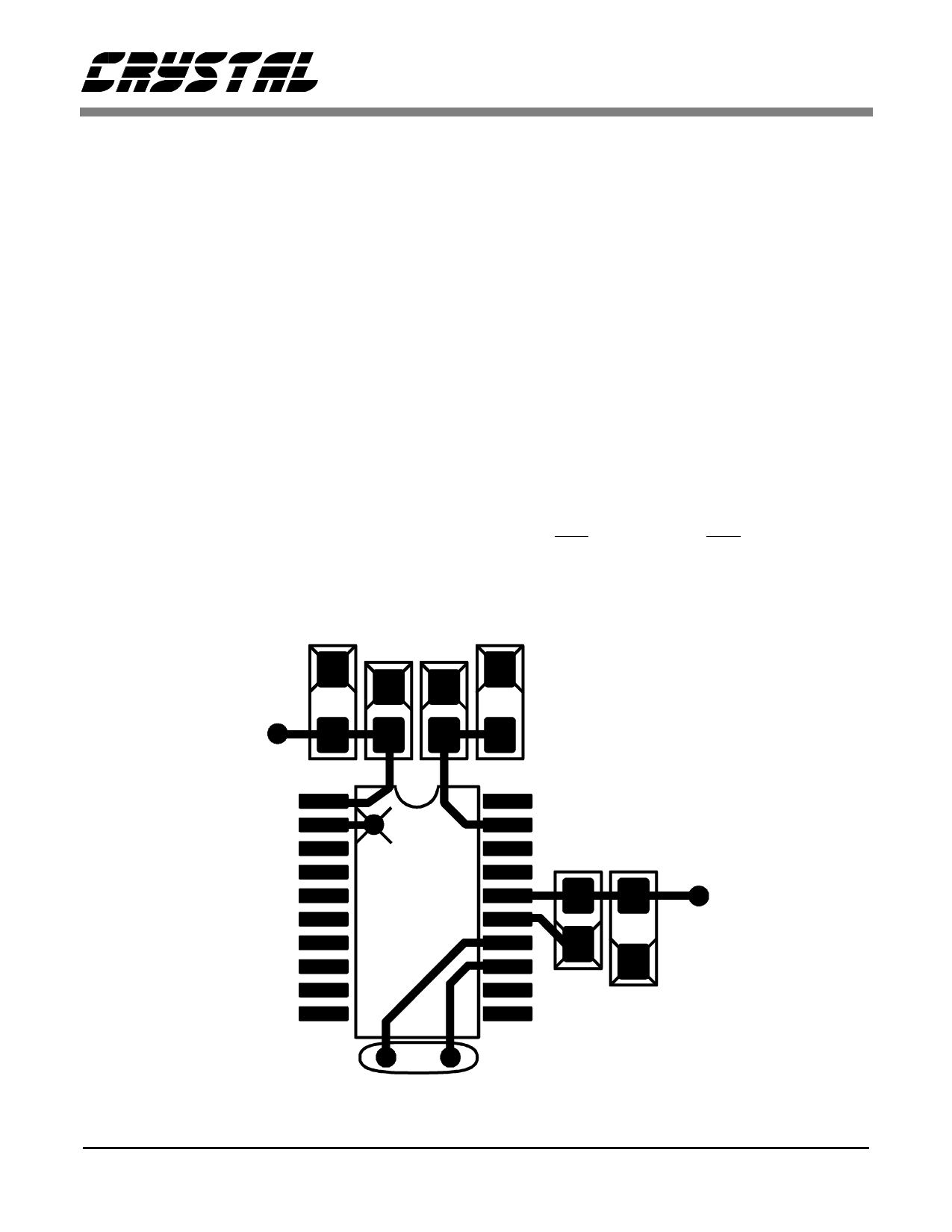

Power Supply

The pins AVDD (pin 1) and AGND (pin 2) power

the analog sections of the CS6420, and DVDD (pin

16) and DGND (pin 15) power the digital sections.

This distinction is important because internal to the

part, the digital power supply is likely to contain

high-frequency energy. The analog power supply is

kept clean internally by drawing current from a dif-

ferent pin, thereby achieving high performance in

the converters.

The digital supply of the CS6420 should not be

connected to the system digital supply, if there is

one, as the CS6420 has internal timing mechanisms

designed to minimize the detrimental effects of its

own digital noise, but cannot use these to compen-

sate for externally introduced digital noise. The

CS6420 digital power supply should be derived

from its analog power supply through a ferrite bead

with low (< 1 Ω) DC impedance.

Power Down Mode

Typical power consumption of the CS6420 is 60

mA, assuming normal operating conditions. This

current consumption can be further reduced by in-

voking the powerdown mode, which is entered by

holding RST low. Holding RST low will power

down all the internal blocks of the CS6420 and stop

the oscillator. In powerdown mode, current con-

sumption drops to less than 1 mA.

+5V

Analog

Supply

AVDD

AGND

MB

DVDD

DGND

From

Ferrite

Bead

Figure 6. Suggested Layout

20

DS205PP2