CS5531-AS Ver la hoja de datos (PDF) - Cirrus Logic

Número de pieza

componentes Descripción

Lista de partido

CS5531-AS Datasheet PDF : 50 Pages

| |||

CS5531/32/33/34-AS

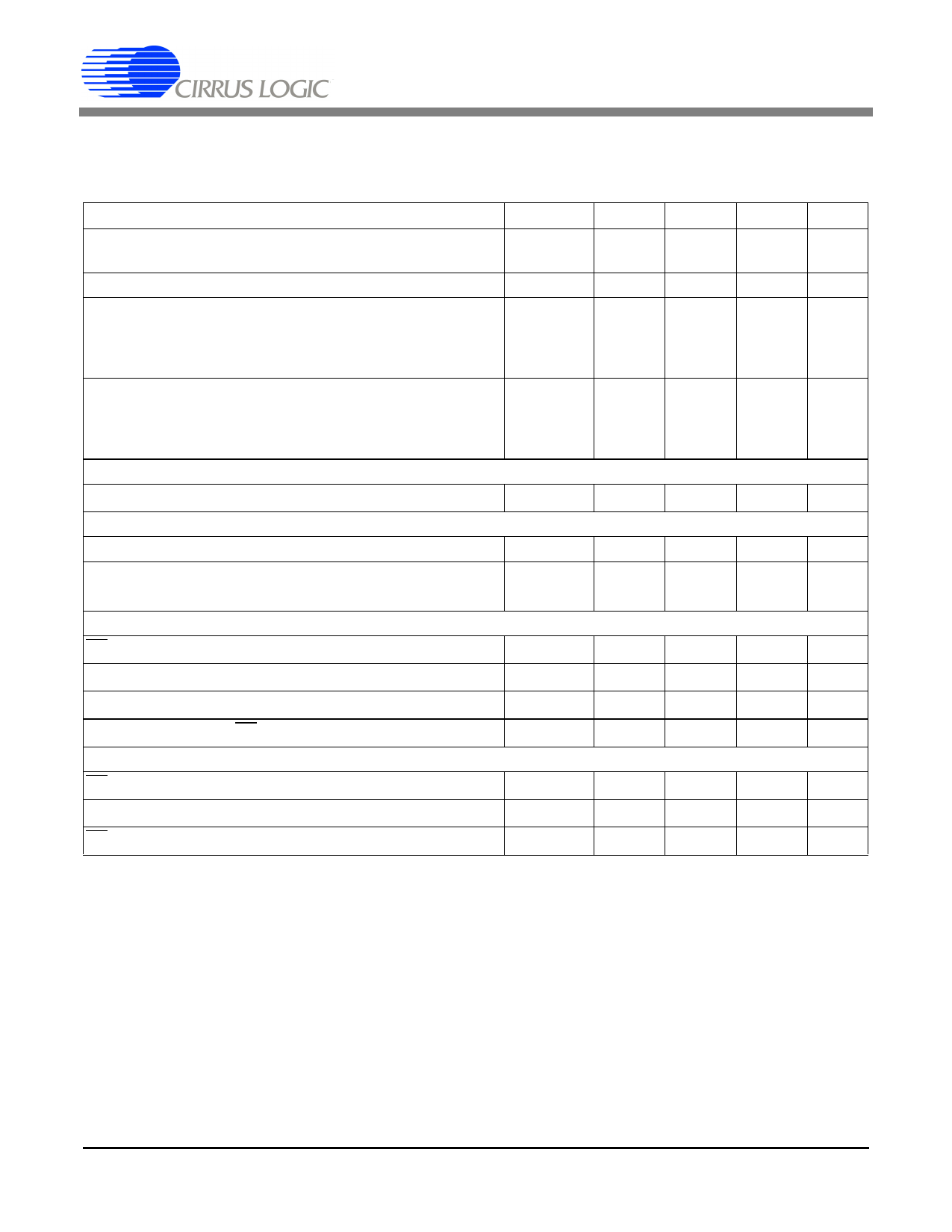

SWITCHING CHARACTERISTICS

(VA+ = 2.5 V or 5 V ±5%; VA- = -2.5V±5% or 0 V; VD+ = 3.0 V ±10% or 5 V ±5%;DGND = 0 V;

Levels: Logic 0 = 0 V, Logic 1 = VD+; CL = 50 pF; See Figures 1 and 2.)

Parameter

Master Clock Frequency

(Note 26)

External Clock or Crystal Oscillator

Master Clock Duty Cycle

Rise Times

(Note 27)

Any Digital Input Except SCLK

SCLK

Any Digital Output

Fall Times

(Note 27)

Any Digital Input Except SCLK

SCLK

Any Digital Output

Start-up

Oscillator Start-up Time XTAL = 4.9152 MHz (Note 28)

Serial Port Timing

Serial Clock Frequency

Serial Clock

Pulse Width High

Pulse Width Low

SDI Write Timing

CS Enable to Valid Latch Clock

Data Set-up Time prior to SCLK rising

Data Hold Time After SCLK Rising

SCLK Falling Prior to CS Disable

SDO Read Timing

CS to Data Valid

SCLK Falling to New Data Bit

CS Rising to SDO Hi-Z

Symbol

MCLK

trise

tfall

tost

SCLK

t1

t2

t3

t4

t5

t6

t7

t8

t9

Min

Typ

Max Unit

1

4.9152

5

MHz

40

-

60

%

-

-

1.0

µs

-

-

100

µs

-

50

-

ns

-

-

1.0

µs

-

-

100

µs

-

50

-

ns

-

20

-

ms

0

-

250

-

250

-

2

MHz

-

ns

-

ns

50

-

50

-

100

-

100

-

-

ns

-

ns

-

ns

-

ns

-

-

150

ns

-

-

150

ns

-

-

150

ns

Notes: 26. Device parameters are specified with a 4.9152 MHz clock.

27. Specified using 10% and 90% points on waveform of interest. Output loaded with 50 pF.

28. Oscillator start-up time varies with crystal parameters. This specification does not apply when using an

external clock source.

10

DS289F5