RTL8208 Ver la hoja de datos (PDF) - Realtek Semiconductor

Número de pieza

componentes Descripción

Lista de partido

RTL8208 Datasheet PDF : 40 Pages

| |||

7. Functional Description

RTL8208

7.1 General

7.1.1 SMI (Serial Management Interface)

SMI (Serial Management Interface) is also known as MII Management Interface, which consists of two signals, MDIO and

MDC; allowing the MAC controller to control and monitor the state of the PHY. MDC is a clock input for PHY to latch MDIO on

its rising edge. The clock can run from DC to 25MHz. MDIO is a bi-directional connection used to write data to, or read data

from PHY. The PHY address base is set by pins PHY_ADDR[4:3] and eight ports addresses of RTL8208 are internally

000,001,010,011,100,101,110,and 111.

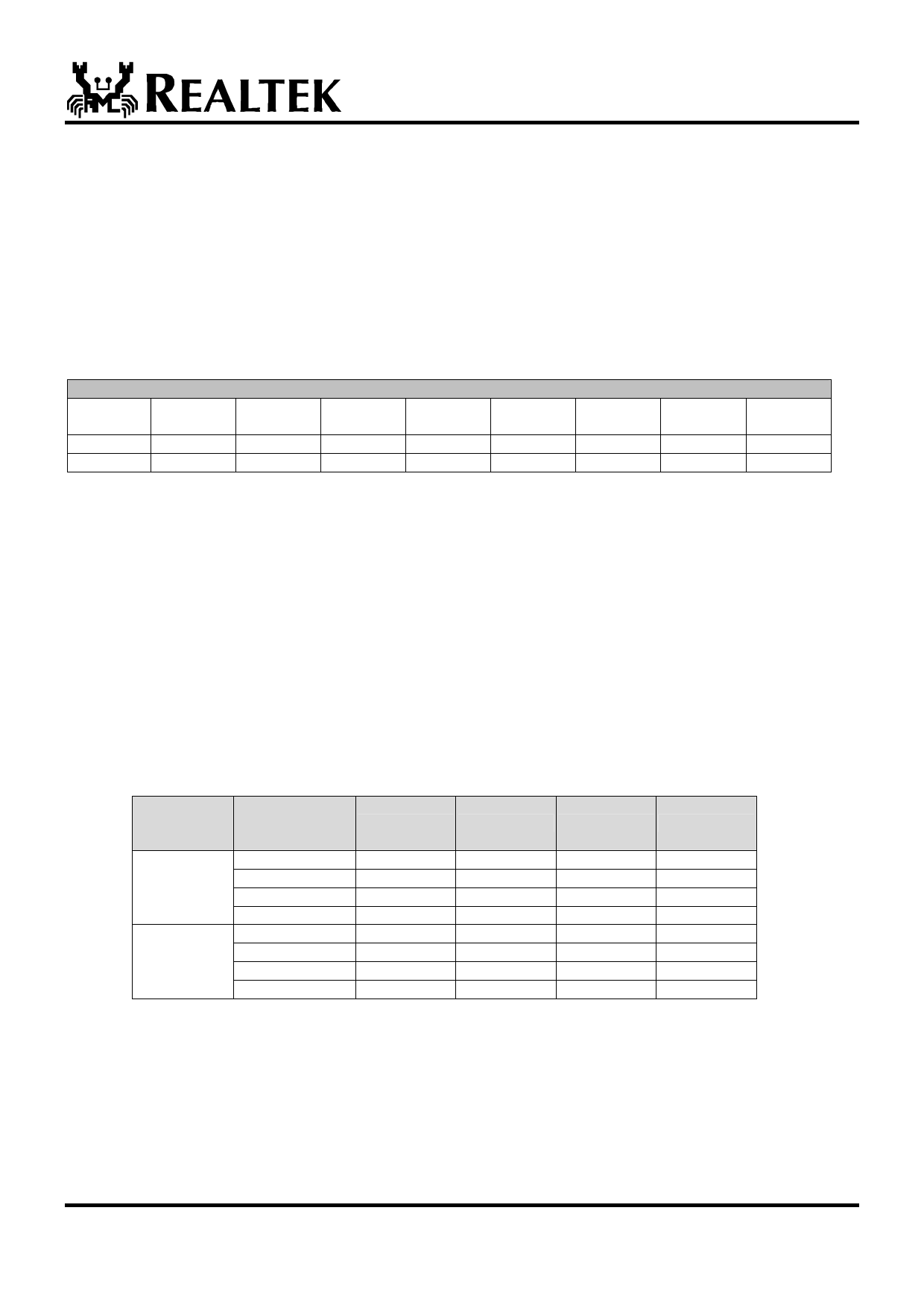

SMI Read/Write Cycles

Preamble Start

OP Code PHYAD REGAD TurnAround Data

Idle

(32 bits) (2 bits) (2 bits)

(5 bits) (5 bits) (2 bits) (16 bits)

Read

1……..1 01

10

AAAAA RRRRR

Z0

D…….D

Z*

Write

1……..1 01

01

AAAAA RRRRR

10

D…….D

Z*

*Z: high-impedance. During idle time, MDIO state is determined by an external 1.5KΩ pull-up resistor.

The RTL8208 supports Preamble Suppression, which allows the MAC to issue Read/Write Cycles without preamble bits (but

needs at least one Idle for every cycle). However, for the first MII management cycle after power-on reset, a 32-bit preamble is

needed. To guarantee the first successful SMI transaction after power-on reset, the MAC should be delayed at least 700us to issue

the first SMI Read/Write Cycle relative to the rising edge of reset.

7.1.2 Port Pair Loop Back Mode (PP-LPBK)

PP-LPBK mode is enabled by pulling pin 81 high on reset. When in PP-LPBK mode, the ports of the RTL8208 is configured as

four pairs, port0 & port1, port2 & port3, port4 & port5, and port 6 & port7. Each pair are set as RMII interface loop back, acting

like a signal regeneration /transformation repeater, so a switch controller is not necessary.

In PP-LPBK mode, TP port and FX port selection is different from that in normal mode. The TP and FX port selection

configuration is as follows:

For this table, “U” means UTP port, “F” means Fiber port.

PP-LPBK SEL_TXFX[1:0]

mode

(Pin 99,107)

(Pin 81)

0

00

(normal mode)

01

10

11

1

00

(PP-LPBK)

01

10

11

Port0, Port1

UU

UU

UU

FF

UU

UU

UF

FF

Port2, Port3

UU

UU

UU

FF

UU

UU

UF

FF

Port4, Port5

UU

UU

UU

FF

UU

UF

UF

FF

Port6, Port7

UU

UF

FF

FF

UU

UF

UF

FF

Since this configuration is a loop back mode, it uses Full duplex only, and Half duplex is not supported. The loop-back-pair ports

should be configured as the same Speed. Although this mode does not effect normal N-Way mode, in order to keep in the same

speed for each pair’s two ports, there is an auto-detection scheme. This scheme specifies that if one port of the pair is already

linked, when the other port is linked later, the earlier link-on port will re-start Auto-negotiation, trying to keep the two ports

linked at the same speed. When PP-LPBK mode is set, there are three requirements: It must be based upon RMII mode; no

switch controller is connected; and TX_EN[7:0] is pulled down.

2003/04/04

19

Rev.1.97