IDT72205LB Ver la hoja de datos (PDF) - Integrated Device Technology

Número de pieza

componentes Descripción

Lista de partido

IDT72205LB

IDT72205LB Datasheet PDF : 21 Pages

| |||

IDT72205LB/72215LB/72225LB/72235LB/72245LB CMOS SyncFIFO™

256 x 18-BIT, 512 x 18, 1024 x 18, 2048 x 18 and 4096 x 18

MILITARY AND COMMERCIAL TEMPERATURE RANGES

m) writes for the IDT72205LB, (512-m) writes for the

IDT72215LB, (1024-m) writes for the IDT72225LB, (2048–m)

writes for the IDT72235LB and (4096–m) writes for the

IDT72245LB. The offset “m” is defined in the FULL offset

register.

If there is no Full offset specified, the PAF will be LOW when

the device is 31 away from completely full for 72205LB, 63

away from completely full for 72215LB, and 127 away from

completely full for 72225LB/72235LB/72245LB.

The PAF is asserted LOW on the LOW-to-HIGH transition

of the write clock (WCLK). PAF is reset to HIGH on the LOW-

to-HIGH transition of the read clock (RCLK). Thus PAF is

asychronous.

PROGRAMMABLE ALMOST-EMPTY FLAG (PAE)

The Programmable Almost-Empty Flag (PAE) will go LOW

when the read pointer is “n+1” locations less than the write

pointer. The offset “n” is defined in the EMPTY offset register.

If there is no Empty offset specified, the Programmable

Almost Empty Flag (PAE) will be LOW when the device is 31

away from completely empty for 72205LB, 63 away from

completely empty for 72215LB, and 127 away from com-

pletely empty for 72225LB/72235LB/72245LB.

The PAE is asserted LOW on the LOW-to-HIGH transition

of the read clock (RCLK). PAE is reset to HIGH on the LOW-

to-HIGH transition of the write clock (WCLK). Thus PAF is

asychronous.

WRITE EXPANSION OUT/HALF-FULL FLAG (WXO/HF)

This is a dual-purpose output. In the Single Device and

Width Expansion mode, when Write Expansion In (WXI) is

grounded, this output acts as an indication of a half-full

memory.

After half of the memory is filled, and at the LOW-to-HIGH

transition of the next write cycle, the Half-Full Flag goes LOW

and will remain set until the difference between the write

pointer and read pointer is less than or equal to one half of the

total memory of the device. The Half-Full Flag (HF) is then reset

to HIGH by the LOW-to-HIGH transition of the read clock

(RCLK). The HF is asychronous.

In the Depth Expansion or Daisy Chain mode, WXI is

connected to WXO of the previous device. This output acts as

a signal to the next device in the Daisy Chain by providing a

pulse when the previous device writes to the last location of

memory.

READ EXPANSION OUT (RXO)

In the Depth Expansion or Daisy Chain configuration, Read

Expansion In (RXI) is connected to Read Expansion Out

(RXO) of the previous device. This output acts as a signal to

the next device in the Daisy Chain by providing a pulse when

the previous device reads from the last location of memory.

DATA OUTPUTS (Q0-Q17)

Q0-Q17 are data outputs for 18-bit wide data.

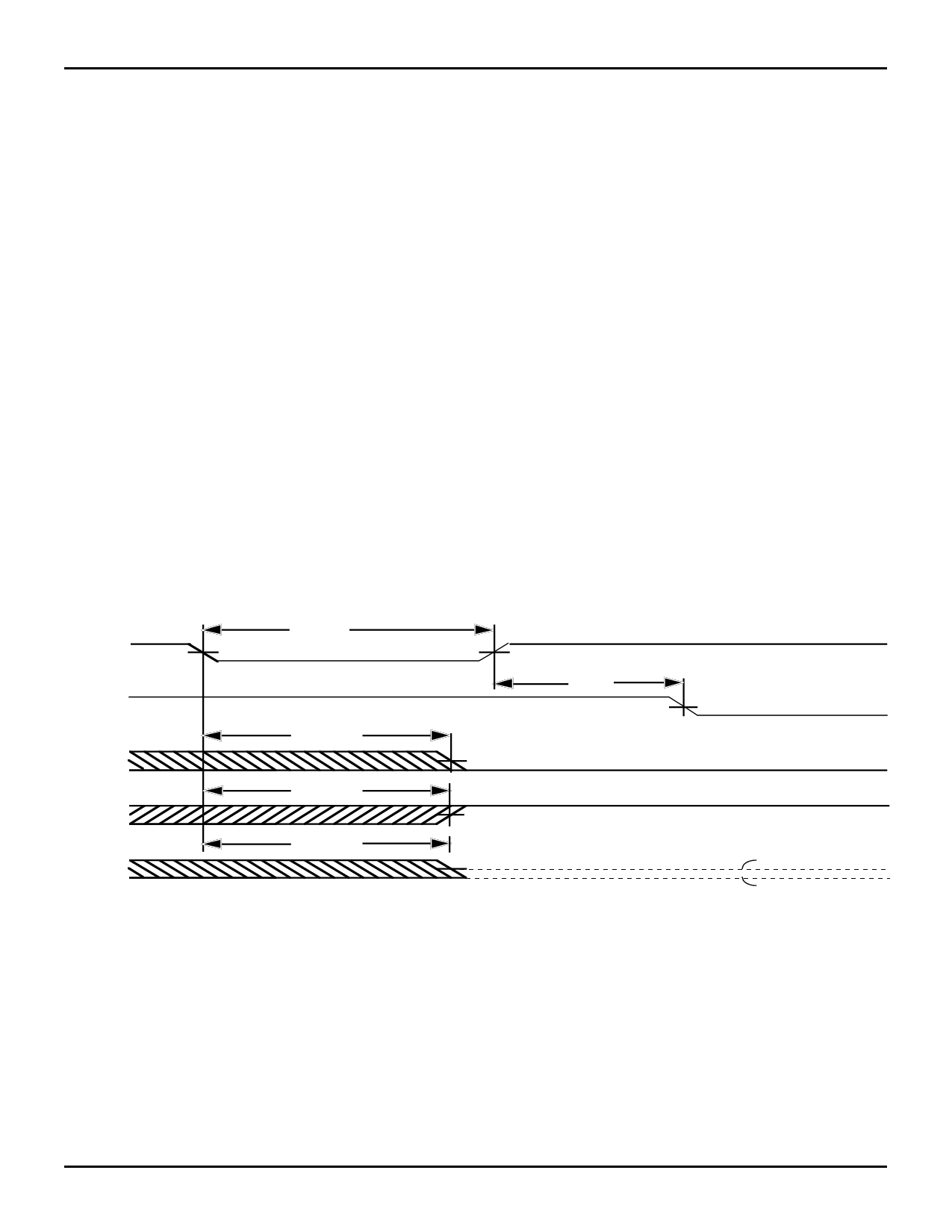

RS

t RS

REN,

WEN, LD

t RSF

EF , PAE

FF,

PAF,HF

Q0 - Q17

t RSF

t RSF

t RSR

NOTES:

1. After reset, the outputs will be LOW if OE = 0 and tri-state if OE = 1.

2. The clocks (RCLK, WCLK) can be free-running during reset.

Figure 5. Reset Timing(2)

OE = 1(1)

OE = 0

5.16

9