IDT72265LA Ver la hoja de datos (PDF) - Integrated Device Technology

Número de pieza

componentes Descripción

Lista de partido

IDT72265LA Datasheet PDF : 27 Pages

| |||

IDT72255LA/72265LA SUPERSYNC FIFO™

8,192 x 18, 16,384 x 18

COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGE

DESCRIPTION (Continued)

• The first word data latency period, from the time the first

word is written to an empty FIFO to the time it can be read,

is now fixed and short. (The variable clock cycle counting

delay associated with the latency period found on previous

SuperSync devices has been eliminated on this SuperSync

family.)

SuperSync FIFOs are particularly appropriate for network,

video, telecommunications, data communications and other

applications that need to buffer large amounts of data.

The input port is controlled by a Write Clock (WCLK) input

and a Write Enable (WEN) input. Data is written into the FIFO

on every rising edge of WCLK when WEN is asserted. The

output port is controlled by a Read Clock (RCLK) input and

Read Enable (REN) input. Data is read from the FIFO on every

rising edge of RCLK when REN is asserted. An Output Enable

(OE) input is provided for three-state control of the outputs.

The frequencies of both the RCLK and the WCLK signals

may vary from 0 to fMAX with complete independence. There

are no restrictions on the frequency of one clock input with

respect to the other.

There are two possible timing modes of operation with

these devices: IDT Standard mode and First Word Fall Through

(FWFT) mode.

In IDT Standard mode, the first word written to an empty

FIFO will not appear on the data output lines unless a specific

read operation is performed. A read operation, which consists

of activating REN and enabling a rising RCLK edge, will shift

the word from internal memory to the data output lines.

In FWFT mode, the first word written to an empty FIFO is

clocked directly to the data output lines after three transitions

of the RCLK signal. A REN does not have to be asserted for

accessing the first word. However, subsequent words written

to the FIFO do require a LOW on REN for access. The state

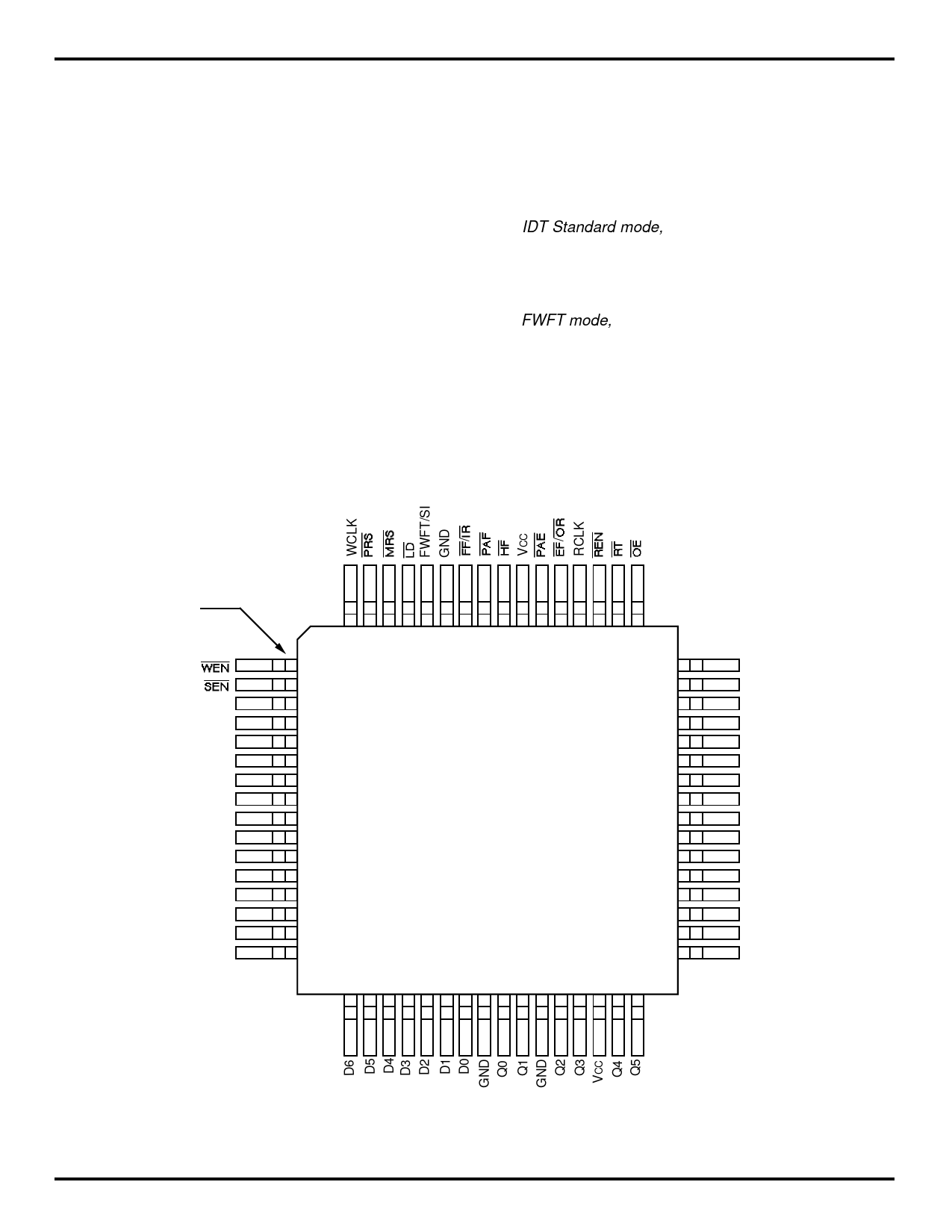

PIN CONFIGURATIONS

PIN 1

DC

VCC

GND

D17

D16

D15

D14

D13

D12

D11

D10

D9

D8

D7

64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49

1

48

2

47

3

46

4

45

5

44

6

43

7

42

8

41

9

40

10

39

11

38

12

37

13

36

14

35

15

34

16

33

17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32

Q17

Q16

GND

Q15

Q14

VCC

Q13

Q12

Q11

GND

Q10

Q9

Q8

Q7

Q6

GND

TQFP (PN64-1, order code: PF)

STQFP (PP64-1, order code: TF)

TOP VIEW

4670 drw 02

2