ISP1181A Ver la hoja de datos (PDF) - Philips Electronics

Número de pieza

componentes Descripción

Lista de partido

ISP1181A Datasheet PDF : 70 Pages

| |||

Philips Semiconductors

ISP1181A

Full-speed USB peripheral controller

8. Modes of operation

The ISP1181A has four bus configuration modes, selected via pins BUS_CONF1 and

BUS_CONF0:

Mode 0

Mode 1

Mode 2

Mode 3

16-bit I/O port shared with 16-bit DMA port

reserved

8-bit I/O port shared with 8-bit DMA port

reserved.

The bus configurations for each of these modes are given in Table 3. Typical interface

circuits for each mode are given in Section 21.1.

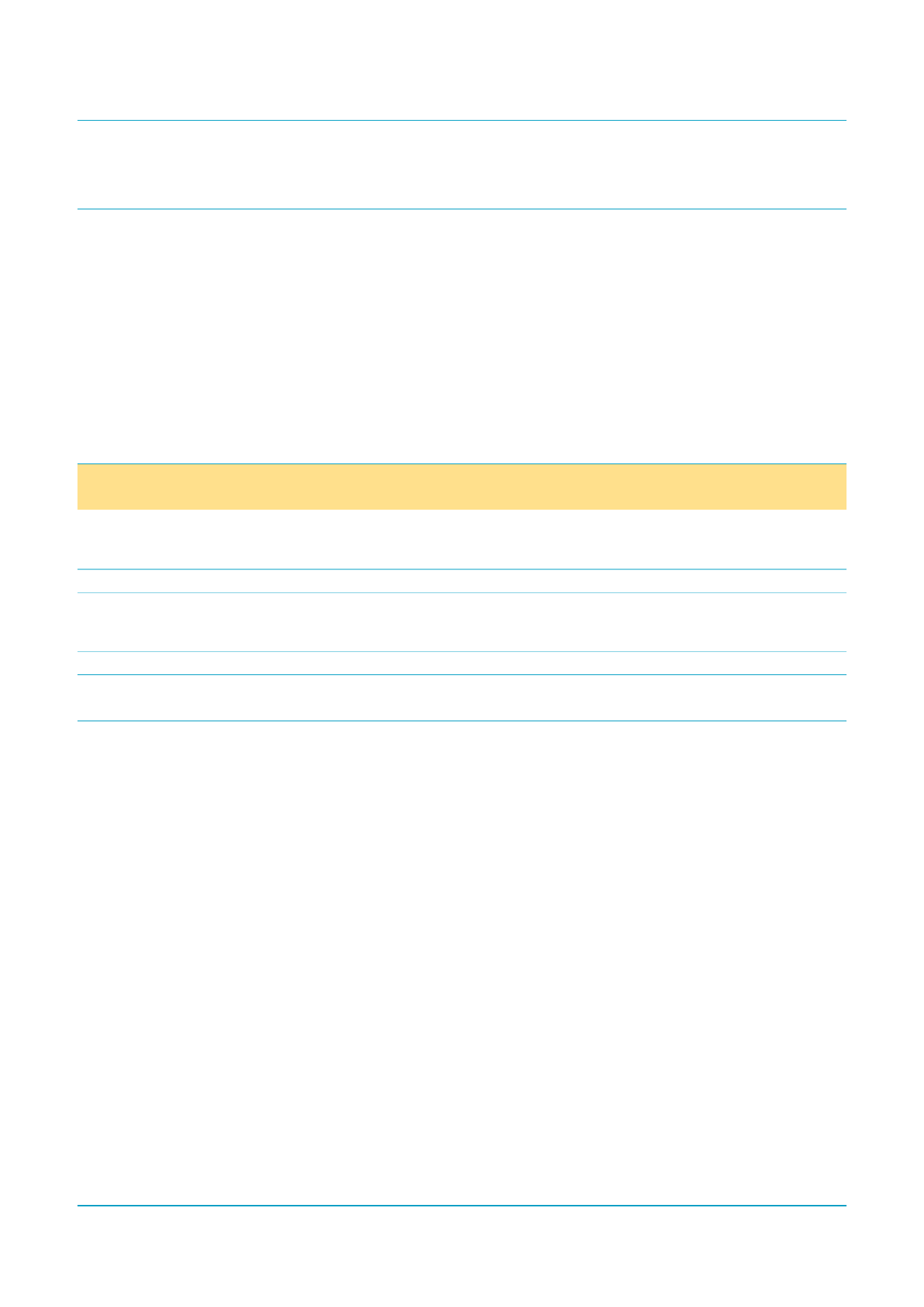

Table 3:

Mode

0

1

2

3

Bus configuration modes

BUS_CONF[1:0] PIO width

0

0 D[15:1], AD0

0

1 reserved

1

0 D[7:1], AD0

1

1 reserved

DMA width

DMAWD = 0 DMAWD = 1

-

D[15:1], AD0

reserved

D[7:1], AD0

reserved

-

reserved

reserved

Description

multiplexed address/data on pin AD0;

bus is shared by 16-bit I/O port and

16-bit DMA port

reserved

multiplexed address/data on pin AD0;

bus is shared by 8-bit I/O port and 8-bit

DMA port

reserved

9. Endpoint descriptions

Each USB peripheral is logically composed of several independent endpoints. An

endpoint acts as a terminus of a communication flow between the host and the

peripheral. At design time each endpoint is assigned a unique number (endpoint

identifier, see Table 4). The combination of the peripheral address (given by the host

during enumeration), the endpoint number, and the transfer direction allows each

endpoint to be uniquely referenced.

The ISP1181A has 16 endpoints: endpoint 0 (control IN and OUT) plus 14

configurable endpoints, which can be individually defined as

interrupt/bulk/isochronous, IN or OUT. Each enabled endpoint has an associated

FIFO, which can be accessed either via the parallel I/O interface or via DMA.

9.1 Endpoint access

Table 4 lists the endpoint access modes and programmability. All endpoints support

I/O mode access. Endpoints 1 to 14 also support DMA access. FIFO DMA access is

selected and enabled via bits EPIDX[3:0] and DMAEN of the DMA Configuration

Register. A detailed description of the DMA operation is given in Section 10.

9397 750 13959

Product data

Rev. 05 — 08 December 2004

© Koninklijke Philips Electronics N.V. 2004. All rights reserved.

11 of 70