RTL8101 Ver la hoja de datos (PDF) - Unspecified

Número de pieza

componentes Descripción

Lista de partido

RTL8101 Datasheet PDF : 68 Pages

| |||

RTL8101L

3

R/W

RE

Receiver Enable: When set to 1, and the receive state machine is idle,

the receive machine becomes active. This bit will read back as a 1

whenever the receive state machine is active. After initial power-up,

software must insure that the receiver has completely reset before setting

this bit.

2

R/W

TE

Transmitter Enable: When set to 1, and the transmit state machine is

idle, then the transmit state machine becomes active. This bit will read

back as a 1 whenever the transmit state machine is active. After initial

power-up, software must insure that the transmitter has completely reset

before setting this bit.

1

-

-

Reserved

0

R

BUFE

Buffer Empty: Rx Buffer Empty. There is no packet stored in the Rx

buffer ring.

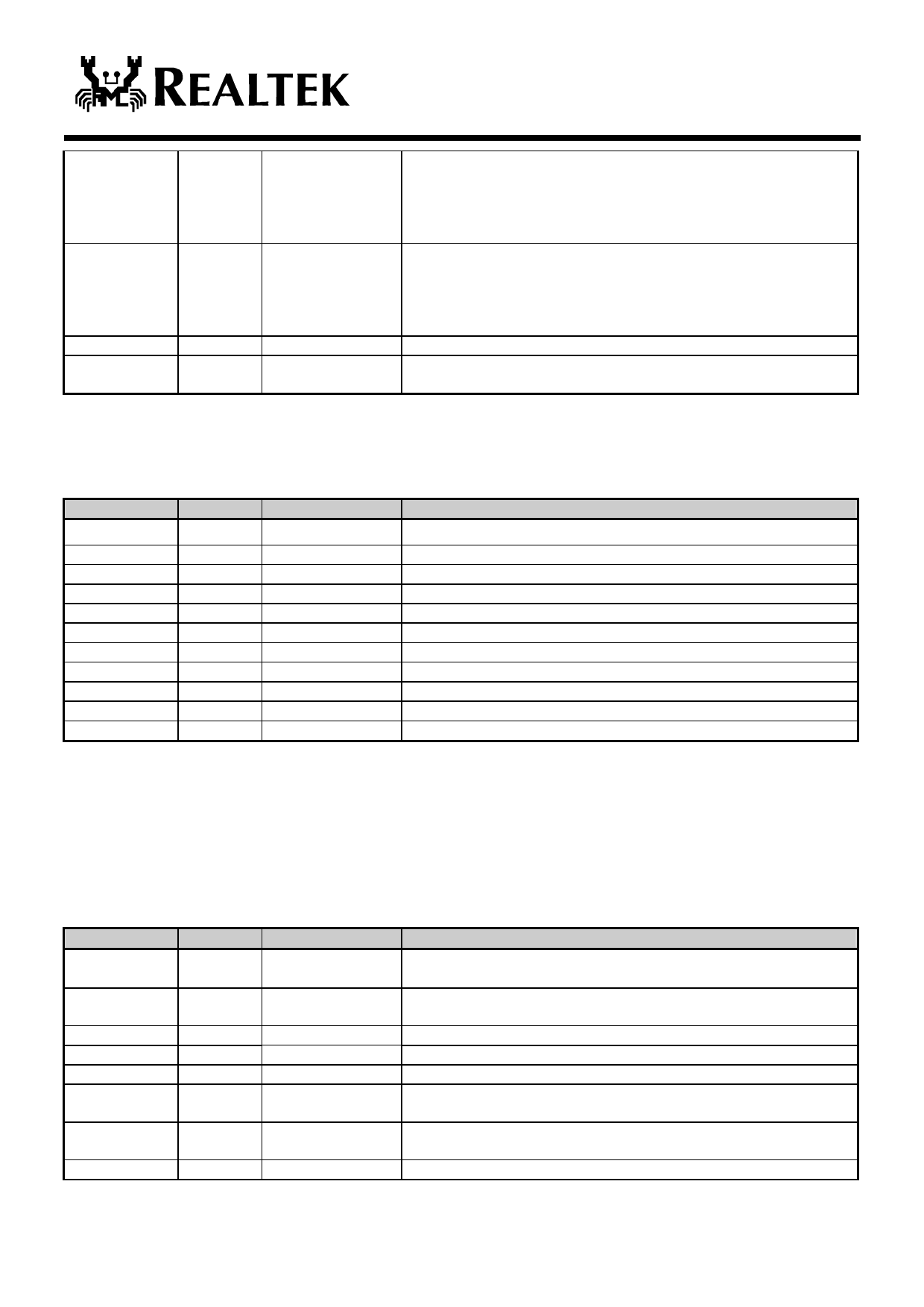

5.5 Interrupt Mask Register

(Offset 003Ch-003Dh, R/W)

Bit

R/W

Symbol

Description

15

R/W

SERR

System error Interrupt: 1 => Enable, 0 => Disable.

14

R/W

TimeOut

Time Out Interrupt: 1 => Enable, 0 => Disable.

13

R/W

LenChg

Cable Length Change Interrupt: 1 => Enable, 0 => Disable.

12-7

-

-

Reserved

6

R/W

FOVW

Rx FIFO Overflow Interrupt: 1 => Enable, 0 => Disable.

5

R/W

PUN/LinkChg Packet Underrun/Link Change Interrupt: 1 => Enable, 0 => Disable.

4

R/W

RXOVW

Rx Buffer Overflow Interrupt: 1 => Enable, 0 => Disable.

3

R/W

TER

Transmit error Interrupt: 1 => Enable, 0 => Disable.

2

R/W

TOK

Transmit OK Interrupt: 1 => Enable, 0 => Disable.

1

R/W

RER

Receive Error Interrupt: 1 => Enable, 0 => Disable.

0

R/W

ROK

Receive OK Interrupt: 1 => Enable, 0 => Disable.

5.6 Interrupt Status Register

(Offset 003Eh-003Fh, R/W)

This register indicates the source of an interrupt when the INTA pin goes active. Enabling the corresponding bits in the Interrupt

Mask Register (IMR) allows bits in this register to produce an interrupt. When an interrupt is active, one of more bits in this

register are set to a “1”. The interrupt Status Register reflects all current pending interrupts, regardless of the state of the

corresponding mask bit in the IMR. Reading the ISR clears all interrupts. Writing to the ISR has no effect.

Bit

15

14

13

12 - 7

6

5

4

3

R/W

R/W

R/W

R/W

-

R/W

R/W

R/W

R/W

Symbol

SERR

TimeOut

LenChg

-

FOVW

PUN/LinkChg

RXOVW

TER

Description

System Error: Set to 1 when the RTL8101L signals a system error on

the PCI bus.

Time Out: Set to 1 when the TCTR register reaches to the value of the

TimerInt register.

Cable Length Change: Cable length is changed after Receiver is enabled.

Reserved

Rx FIFO Overflow: Set when an overflow occurs on the Rx status FIFO.

Packet Underrun/Link Change: Set to 1 when CAPR is written but Rx

buffer is empty, or when link status is changed.

Rx Buffer Overflow: Set when receive (Rx) buffer ring storage

resources have been exhausted.

Transmit (Tx) Error: Indicates that a packet transmission was aborted,

2003-05-28

15

Rev.1.3