SC92031 Ver la hoja de datos (PDF) - Silan Microelectronics

Número de pieza

componentes Descripción

Lista de partido

SC92031

SC92031 Datasheet PDF : 38 Pages

| |||

SC92031

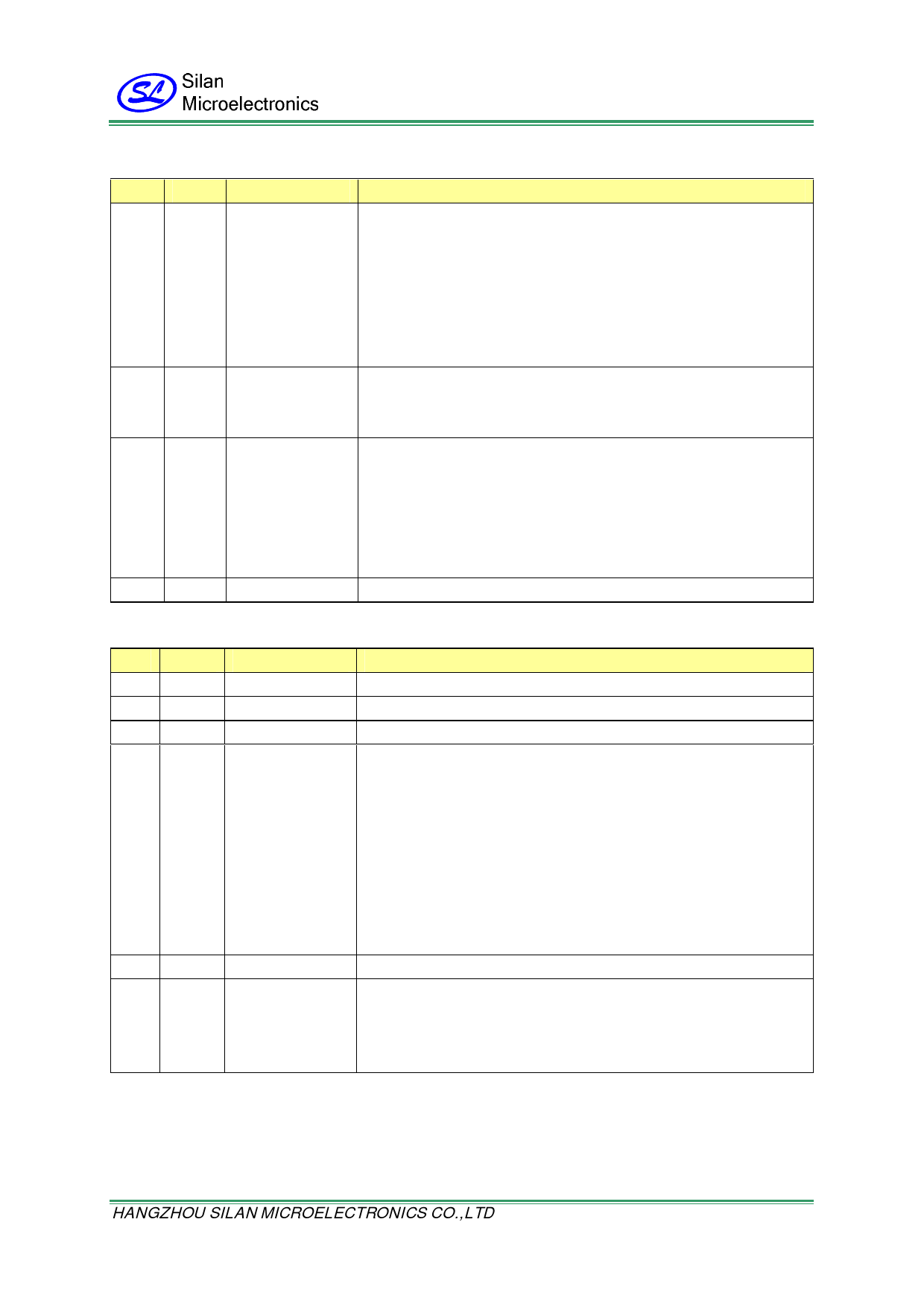

1 Config 0: Configuration Register 0 (Offset 0000h, R/W)

Bit R/W

Symbol

Description

Reset: Setting to 1 forces the chip to a software reset state which

disables the transmitter and receiver, reinitializes the FIFOs, resets the

system buffer pointer to the initial value (Tx buffer is at TSAD0, Rx

31

R/W Software Reset

buffer is empty). The values of IDR0-5 and MAR0-7 and PCI

configuration space will have no changes. This bit is 1 during the reset

operation, and is cleared to 0 by the driver when the reset operation is

complete.

Analog Power

30

R/W

Down

Analog Power Down:

1: Turn off the analog power of the chip internally.

0: Normal working state. This is also power-on default value.

Power Saving Mode:

1: Disable.

29

R/W Power Saving

0: Enable. When cable is disconnected, the analog part will power

down itself automatically except PHY Rx part and part of twister to

monitor SD signal in case that cable is re-connected and Link should

be established again.

28-0

-

-

Reserved

2 Config 1: Configuration Register 1 (Offset 0004h, R/W)

Bit R/W

Symbol

Description

31 R/W Early Reception Set to 1 indicates enable early reception

30 R/W Early Transmission Set to 1 enable early transmission when reach TX threshold

29-24

-

-

Reserved

Rx FIFO Threshold: Specifies Rx FIFO Threshold level. When the

number of the received data bytes from a packet, which is being

received into Rx FIFO, has reached to this level (or the FIFO has

contained a complete packet), the receive PCI bus master function will

23-21 R/W Rx FIFO Threshold begin to transfer the data from the FIFO to the host memory. This field

sets the threshold level according to the following fomula:

Threshold_Level = 16 * 2 ** Rx_FIFO_Threshold

The chip begins the transfer of data after having received a whole

packet in the FIFO.

20-4

-

-

Reserved

Rx Buffer Length: This field indicates the size of the Rx ring buffer.

0000 = 8k Bytes

3-0 R/W Rx Buffer Length

0011 = 32k Bytes

0001 = 16k Bytes

0111 = 64k Bytes

1111 = 128k Bytes

HANGZHOU SILAN MICROELECTRONICS CO.,LTD

Http: www.silan.com.cn

REV:1.0 2004.08.03

Page 9 of 38