Q67100-H6440 Ver la hoja de datos (PDF) - Siemens AG

Número de pieza

componentes Descripción

Lista de partido

Q67100-H6440 Datasheet PDF : 253 Pages

| |||

SAB 82538

SAF 82538

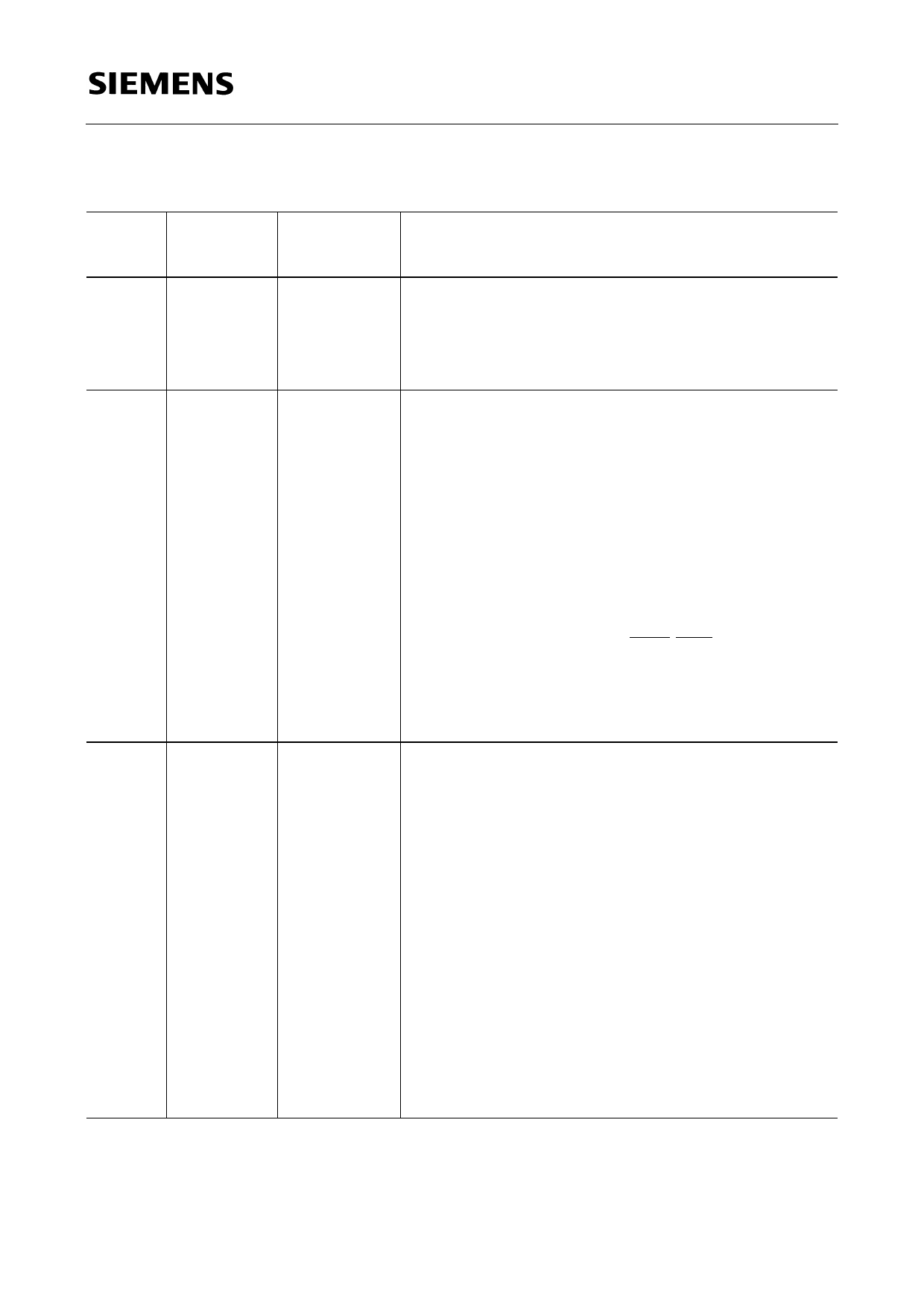

1.1 Pin Definitions and Function

Pin No. Symbol

Input (I)

Function

Output (O)

92 … 84 A0 … A8 I

Address Bus

These inputs interface with nine bits of the

system’s address bus to select one of the internal

registers for read or write.

23 … 30, D0 … D15 I/O

33 … 40

Data Bus

Bi-directional three-state data lines which

interface with the system’s data bus. Their

configuration is controlled by the level of pin

WIDTH:

– 8-bit mode (WIDTH = 0): D0 … D7 are active.

D8 … D15 are in high impedance and have to

be connected to VDD or VSS.

– 16-bit mode (WIDTH = 1): D8…D15 are active.

In case of byte transfers, the active half of the bus

is determined by A0 and BHE/BLE and the

selected bus interface mode (via ALE). The

unused half is in high impedance.

For detailed information, refer to chapter 2.2.1.

97

ALE

I

Address Latch Enable

The level at this pin defines the bus interface

mode:

Fixed to “0”:

Demultiplexed Siemens/Intel bus interface

Fixed to “1”:

Demultiplexed Motorola bus interface

Switching:

Multiplexed Siemens/Intel bus interface

The address information provided on lines

A0 … A8 is internally latched with the falling edge

of ALE. This function allows the ESCC8 to be

directly connected to a multiplexed address/data

bus. In this case, pins A0 … A8 must be externally

connected to the Data Bus pins.

Note: All unused input pins have to be connected to a defined level

Semiconductor Group

11