RTL8139D Ver la hoja de datos (PDF) - Unspecified

Número de pieza

componentes Descripción

Lista de partido

RTL8139D Datasheet PDF : 67 Pages

| |||

Bit

16

15-11

10-8

7-4

3-1

0

R/W

R/W

-

R/W

R/W

-

W

RTL8139DL

Datasheet

Symbol

CRC

-

MXDMA2, 1, 0

TXRR

-

CLRABT

Description

Append CRC: Setting to 1 means that there is no CRC appended at the

end of a packet. Setting to 0 means that there is CRC appended at the

end of a packet.

Reserved

Max DMA Burst Size per Tx DMA Burst: This field sets the

maximum size of transmit DMA data bursts according to the following

table:

000 = 16 bytes

001 = 32 bytes

010 = 64 bytes

011 = 128 bytes

100 = 256 bytes

101 = 512 bytes

110 = 1024 bytes

111 = 2048 bytes

Tx Retry Count: These are used to specify additional transmission

retries in multiple of 16(IEEE 802.3 CSMA/CD retry count). If the

TXRR is set to 0, the transmitter will re-transmit 16 times before

aborting due to excessive collisions. If the TXRR is set to a value

greater than 0, the transmitter will re-transmit a number of times equals

to the following formula before aborting:

Total retries = 16 + (TXRR * 16)

The TER bit in the ISR register or transmit descriptor will be set when

the transmission fails and reaches to this specified retry count.

Reserved

Clear Abort: Setting this bit to 1 causes the RTL8139D(L) to

retransmit the packet at the last transmitted descriptor when this

transmission was aborted, Setting this bit is only permitted in the

transmit abort state.

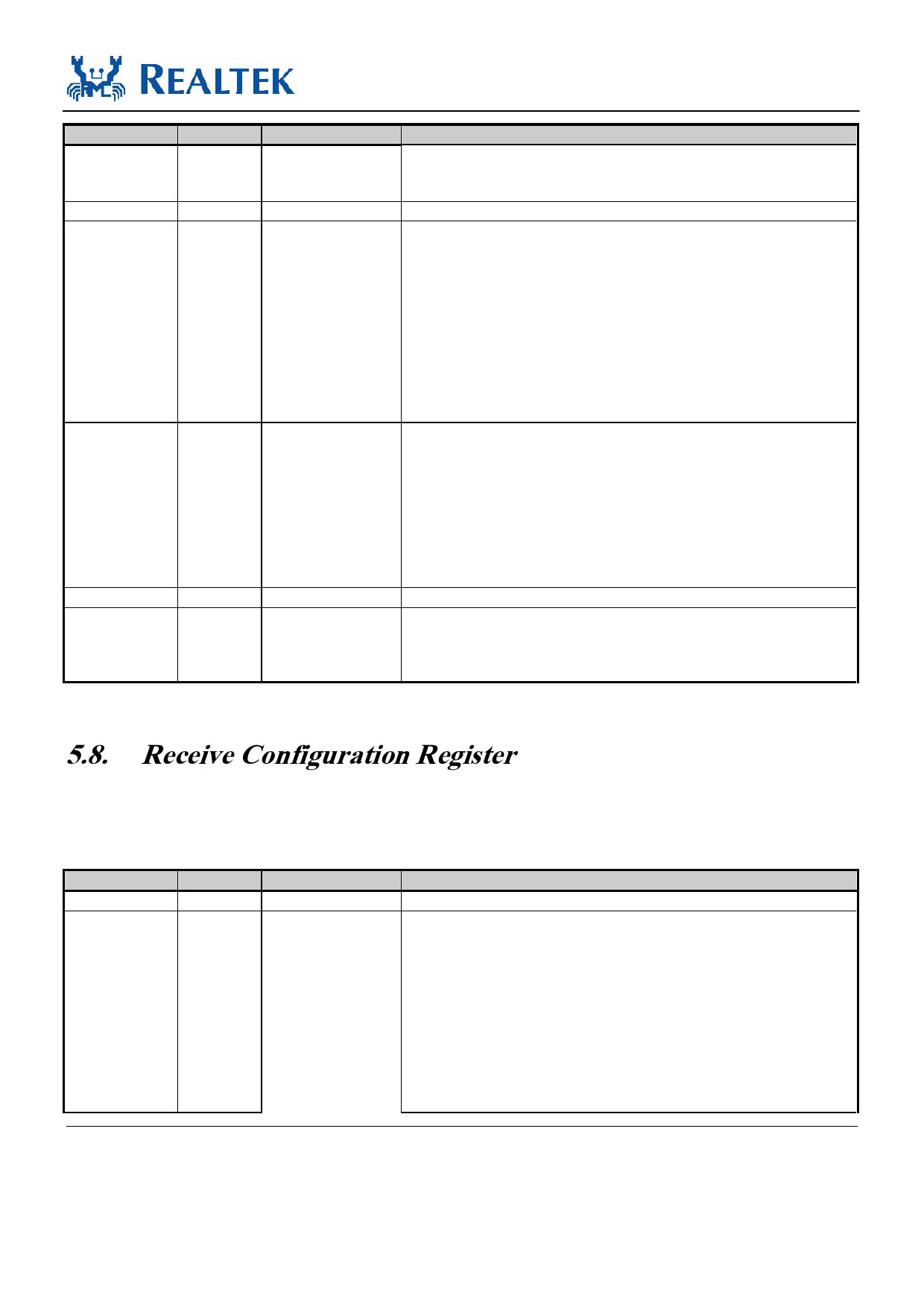

5.8. Receive Configuration Register

(Offset 0044h-0047h, R/W)

This register is used to set the receive configuration for the RTL8139D(L). Receive properties such as

accepting error packets, runt packets, setting the receive drain threshold etc. are controlled here.

Bit

31-28

27-24

R/W

-

R/W

Symbol

-

ERTH3, 2, 1, 0

Description

Reserved

Early Rx threshold bits: These bits are used to select the Rx threshold

multiplier of the whole packet that has been transferred to the system

buffer in early mode when the frame protocol is under the

RTL8139D(L)'s definition.

0000 = no early rx threshold

0001 = 1/16

0010 = 2/16

0011 = 3/16

0100 = 4/16

0101 = 5/16

0110 = 6/16

0111 = 7/16

1000 = 8/16

1001 = 9/16

1010 = 10/16

1011 = 11/16

1100 = 12/16

1101 = 13/16

Single Chip Multifunction 10/100 Ethernet Controller w/Power Management 15 Track ID: JATR-1076-21 Rev. 1.2