MT9125AE Ver la hoja de datos (PDF) - Zarlink Semiconductor Inc

Número de pieza

componentes Descripción

Lista de partido

MT9125AE Datasheet PDF : 18 Pages

| |||

CMOS MT9125

®

Dual ADPCM Transcoder

Preliminary Information

Features

• Dual channel full duplex transcoder

• 32 kbit/s and 24 kbit/s ADPCM coding,

• compatible to G.721 & and G.723 (1988) and

ANSI T1.303-1989

• Low power operation, total 25mW typical

• Asynchronous 4.096 MHz master clock

operation

• Transparent ADPCM bypass capability

• Serial interface for both PCM and ADPCM data

streams

• ST-BUS interface supported

• Pin selected µ-law or A-law operation

• Pin selected CCITT or sign-magnitude PCM

coding

• Single 5 volt power supply

• Optional reset value (CCITT Table 3/G.721)

capability

Applications

• Pair gain

• Voice mail systems

• Wireless set base stations

ISSUE 3

Ordering Information

August 1993

MT9125AE

MT9125AP

24 Pin Plastic DIP (600 mil)

28 Pin PLCC

-40 to +85°C

Description

The Dual-channel ADPCM transcoder is a low

power, CMOS device capable of two encoder

functions and two decoder functions. Two 64 kbit/s

PCM channels are compressed into two 32 kbit/s

ADPCM channels, and two 32 kbit/s ADPCM

channels are expanded into two 64 kbit/s PCM

channels. The 32 kbit/s ADPCM transcoding

algorithm utilized conforms to CCITT Recom-

mendation G.721 and ANSI T1.303-1989. The

device also supports a 24 kbit/s (three bit word)

algorithm (CCITT/G.723).

Switching, on-the-fly, between 32 kbit/s and 24 kbit/

s, is possible by toggling the appropriate Mode

Select (MS1-MS4) control pins.

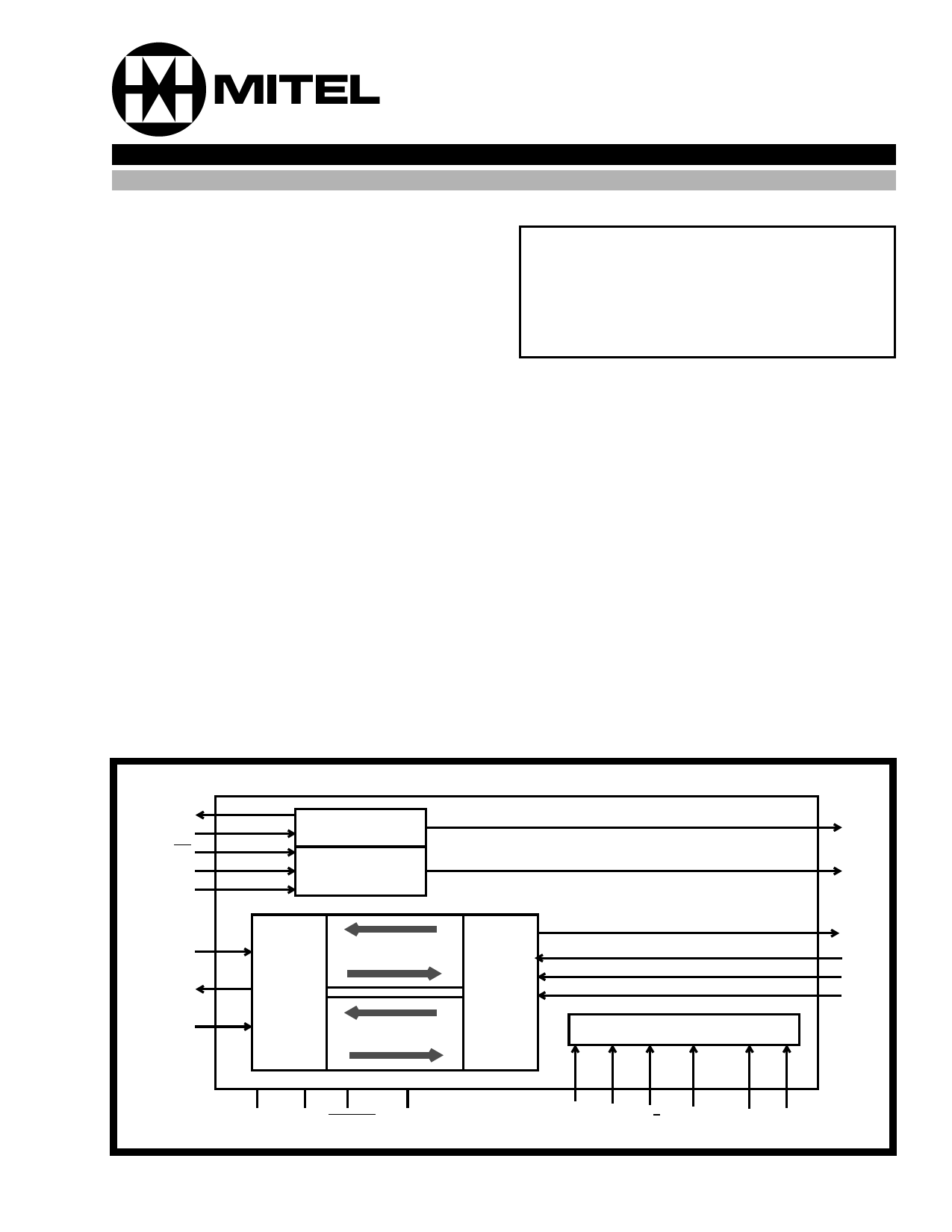

C2o

BCLK

F0i

MCLK

ENS

ADPCMi

ADPCMo

ENA

Timing

ST-BUS

Converter

ADPCM

I/O

Transcoder 1

Transcoder 2

PCM

I/O

Control Decode

EN1

EN2

DSTo

DSTi

ENB1

ENB2

VDD VSS PWRDN IC

MS1 MS2 A/µ FORMAT MS3 MS4

Figure 1 - Functional Block Diagram

8-73