CB35000 Ver la hoja de datos (PDF) - STMicroelectronics

Número de pieza

componentes Descripción

Lista de partido

CB35000 Datasheet PDF : 16 Pages

| |||

CB35000 SERIES

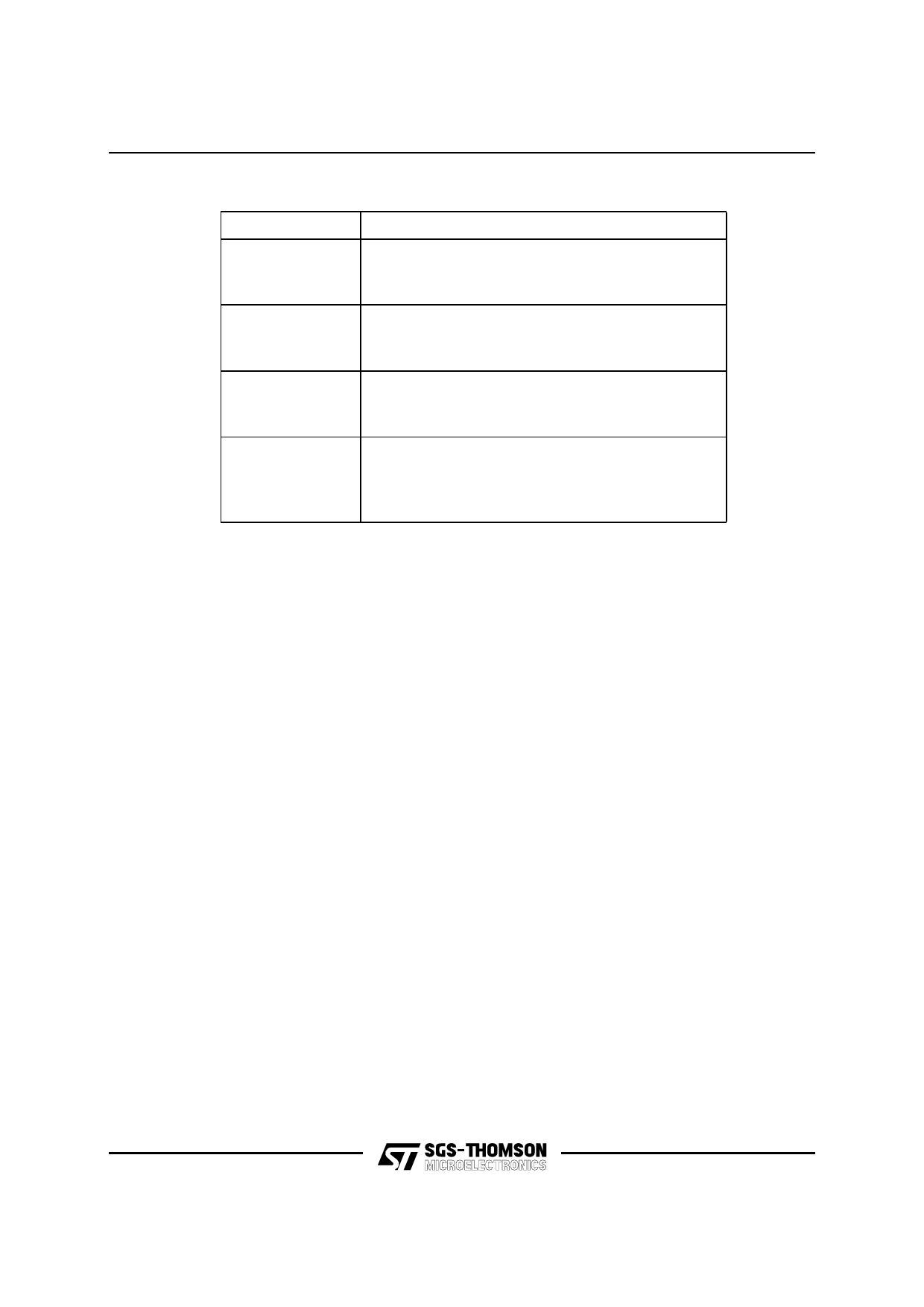

Table 5 Module Generator Library

Cell

Description

SPRAM

256K bits max

16K word max 64 bit max

Zero static current, Tristate outputs

DPRAM

128K bits max

8K word max 64 bit max

Zero static current, Tristate outputs

ROM

2M bits max

32K word max 64 bit max

Diffusion programmable, Tristate outputs

MULT

Parallel asynchronous operation

2’s complement product

6 to 64 bits for both inputs

Ripple Carry or Fast Carry Look Ahead

shift register and adders. Macrofunctions are

implemented at layout by utilizing macrocells and

interconnecting to create the logic function.

MODULE GENERATORS

A series of module generators using compiled

cell generation techniques, are available to

support a range of megacells. These modules

enable the designer to choose individual

parameters in order to create a compiled cell,

which meets the specific application

requirements. These include single port RAM,

dual port RAM, ROM and MULT. The compiled

cell generators construct custom cells, which are

implemented using a special leaf cell technique,

ensuring predictable layout and accurate module

characteristics. In choosing megacells the

designer can consider the trade-offs between

speed and area to generate a fully customized

cell which meets their specific device

requirements. These megacell generators are

complemented by a group of application specific

embedded megacells. These allow access to

technologies that have been hitherto the domain

of standard products. Examples include mixed

mode cells for graphics, DAC/ADC’s (4-9 bit),

PLL applications, and Digital Signal Processor

functions for cellular comms, fax and high-speed

modem.which initially consist of a Triple 8-bit

DAC, Graphics RAM, Clock Multiplier PLL and

Frequency Synthesis PLL.

100 Mbps serial transputer links coupled with

large and fast memory can be used for pipelining,

caching and synchro circuits in modern RISC

computing architectures. Viterbi and Reed

Solomon cores aim at the HDTV and satellite

transmission markets. To support telecom needs

for CCITT standard applications, ADPCM cells

supporting CT2 protocol have been developed.

DESIGN FOR TESTABILITY

The time and cost for ASIC testing increases

exponentially as the complexity and size of the

ASIC grows. Using a design for testability

methodology allows large, more complex ASICs

to be efficiently and economically tested.

CB35000 supports the JTAG boundary Scan and

both edge and level sensitive scan design

techniques by providing the necessary

macrocells. Scan testing aids device testability by

permitting access to internal nodes without

requiring a separate external connection for each

node accessed. Testability is assured at device

level with the close coupling of LSSD latch

elements, Automatic Test Pattern Generation

(ATPG) and high pattern depth tester

architecture. BIST options for memory generators

are also available.

At system level, SGS-THOMSON fully supports

IEEE 1149.1, and the I/O structure utilized in this

family is completely compatible. Several types of

7/16

®