MX98725 Ver la hoja de datos (PDF) - Macronix International

Número de pieza

componentes Descripción

Lista de partido

MX98725 Datasheet PDF : 33 Pages

| |||

MX98725

5. PROGRAMMING INTERFACE

5.1 PCI CONFIGURATION REGISTERS :

5.1.1 PCI ID REGISTER ( PFID ) ( Offset 03h-00h )

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Device ID (bit 31:16)

Vendor ID (bit 15:0)

This register can be loaded from external serial EEPROM or use a MXIC preset value of "0D9" and "0531" for vendor

ID and device ID respectively. Word location 3Eh and 3Dh in serial EEPROM are used to configure customer's

vendor ID and device ID respectively. If location 3Eh contains"FFFF" value then MXIC's vendor ID and device ID will

be set in this register, otherwise both 3Eh and 3Dh will be loaded into this register from serial EEPROM.

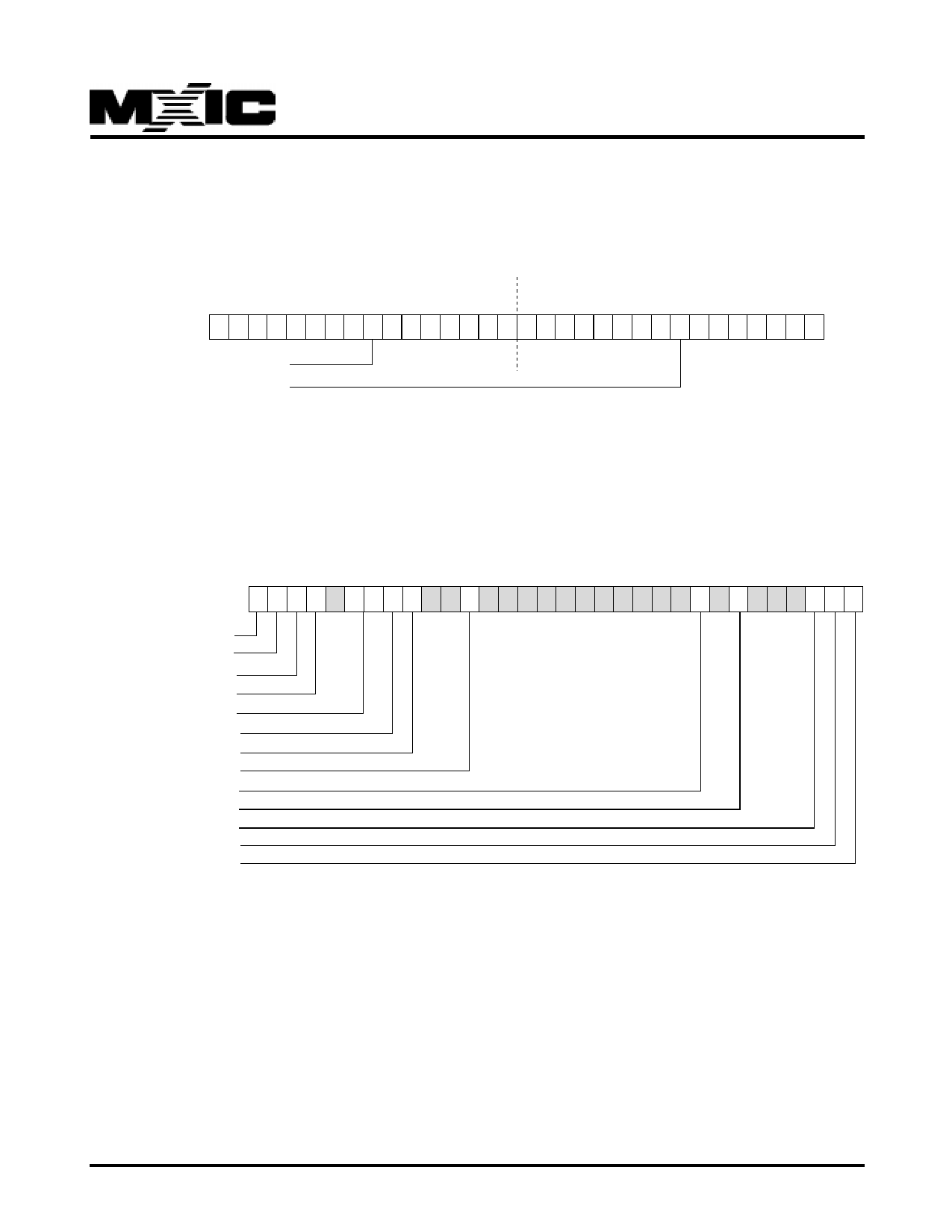

5.1.2 PCI COMMAND AND STATUS REGISTER ( PFCS ) ( Offset 07h-04h )

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Detect Party Error

Signal System Error

Receive Master Abort

Receive Target Abort

Deceive Select Timing

Data Parity Report

Fast Back-to-back

New Capability

System Error Enable

Parity Error Response

Master Operation

Memory Space Access

IO Space Access

The bit content will be reset to 0 when a 1 is written to the corresponding bit location.

bit 0 : IO Space Access, set to 1 enable IO access

bit 1 : Memory Space Access, set to 1 to enable memory access

bit 2 : Master Operation, set to 1 to support bus master mode

bit 5-3 : not used

bit 6 : Parity Error Response, set to 1 to enable assertion of CSR<13> bit if parity error detected.

bit 7 : not used

bit 8 : System Error Enable, set to 1 to enable SERR# when parity error is detected on address lines and CBE[3:0].

bit 20 : New capability. Set to support PCI power management.

bit 22-bit19 : not used

bit 23 : Fast Back-to back, always set to accept fast back-to-back transactions that are not sent to the same bus

device.

P/N:PM0488

REV. 1.7, SEP. 15, 1998

6