DM9102H Ver la hoja de datos (PDF) - Davicom Semiconductor, Inc.

Número de pieza

componentes Descripción

Lista de partido

DM9102H Datasheet PDF : 77 Pages

| |||

DM9102H

Single Chip Fast Ethernet NIC Controller

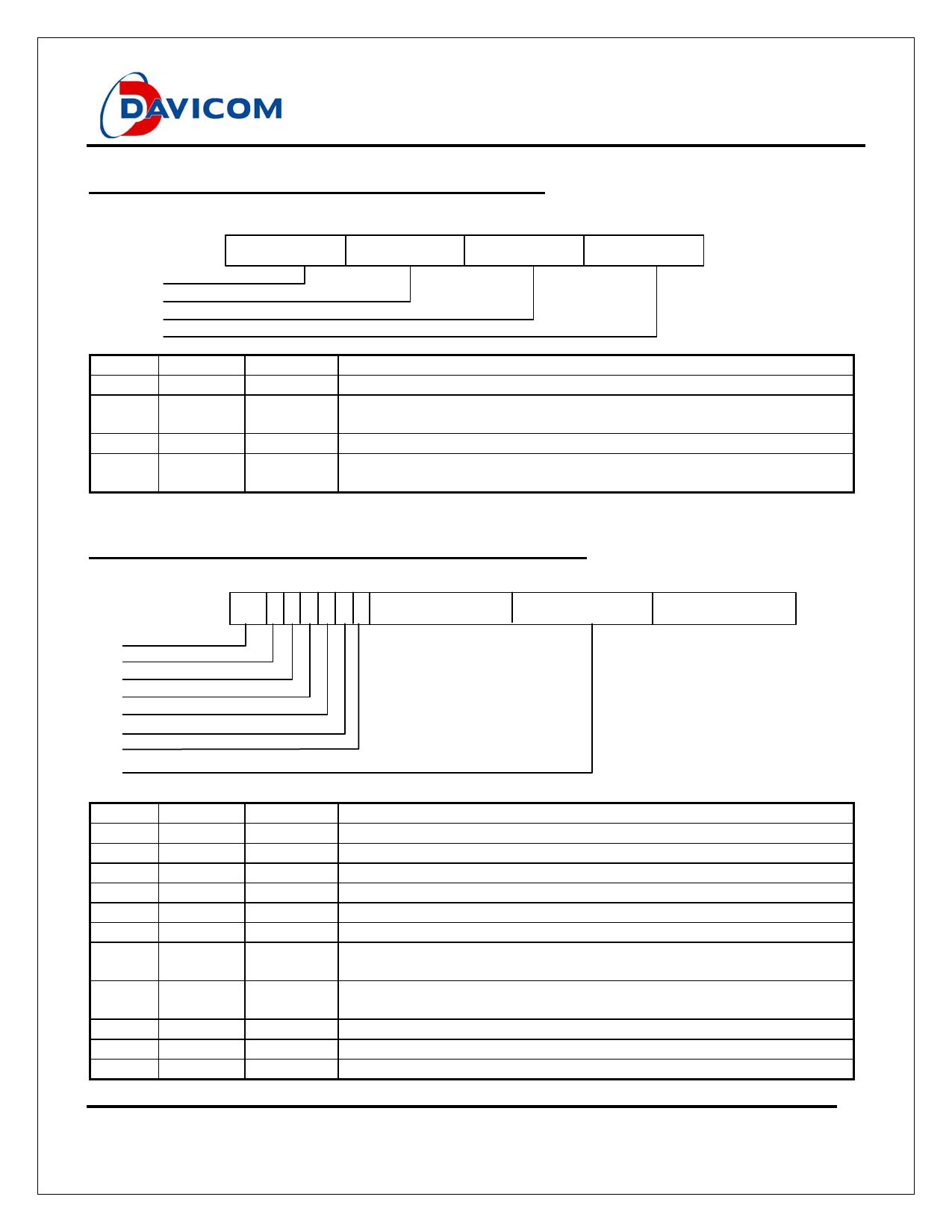

6.1.10 Interrupt & Latency Configuration (xxxxxx3cH - PCIINT)

31

24 23

16 15

MAX_LAT

Maximum Latency Timer

Minimum Grant

Interrupt Pin

Interrupt Line

MIN_GNT

INT_PIN

87

0

INT_LINE

Bit

31:24

23:16

15:8

7:0

Default

28H

14H

01H

XXH

Type

RO

RO

RO

RW

Description

Maximum Latency Timer that can be sustained (Read Only and Read As 28H)

Minimum Grant

Minimum Length of a Burst Period (Read Only and Read As 14H)

Interrupt Pin read as 01H to indicate INTA#

Interrupt Line that Is routed to the Interrupt Controller

The value depends on main board

6.1.11 Device Specific Configuration Register (xxxxxx40H- PCIUSR)

31 30 29 28 27 26 25 24 23

Reserved

16 15

Device Specific

Link Event enable/disable

Sample Frame Event enable/disable

Magic Packet Event enable/disable

Link Event Status

Sample Frame Event Status

Magic Packet Event Status

Device Specific

87

0

Reserved

Bit

31

30

29

28

27

26

25

24

23:16

15:8

7:0

Default

0

0

0

0

0

0

0

0

00H

00H

00H

Type

RW

RW

RW

RW

RW

RO

RO

RO

RO

RW

RO

Description

Device Specific Bit (sleep mode)

Device Specific Bit (snooze mode)

When set, enables Link Status Change Wake up Event

When set, enables Sample Frame Wake up Event

When set, enables Magic Packet Wake up Event

When set, indicates the Link Change and the Link Status Change Event occurred

When set, indicates the Sample Frame is received and the Sample Frame Event

occurred

When set, indicates the Magic Packet is received and the Magic packet Event

occurred

Reserved Bits Read As 0

Device Specific

Reserved Bits Read As 0

Final

15

Version: DM9102H-12-DS-F01

February 15, 2008