PCA9561 Ver la hoja de datos (PDF) - NXP Semiconductors.

Número de pieza

componentes Descripción

Lista de partido

PCA9561 Datasheet PDF : 26 Pages

| |||

NXP Semiconductors

PCA9561

Quad 6-bit multiplexed I2C-bus EEPROM DIP switch

7. Characteristics of the I2C-bus

The I2C-bus is for 2-way, 2-line communication between different ICs or modules. The

two lines are a serial data line (SDA) and a serial clock line (SCL). Both lines must be

connected to a positive supply via a pull-up resistor when connected to the output stages

of a device. Data transfer may be initiated only when the bus is not busy.

7.1 Bit transfer

One data bit is transferred during each clock pulse. The data on the SDA line must remain

stable during the HIGH period of the clock pulse as changes in the data line at this time

will be interpreted as control signals (see Figure 5).

SDA

SCL

Fig 5. Bit transfer

data line

stable;

data valid

change

of data

allowed

mba607

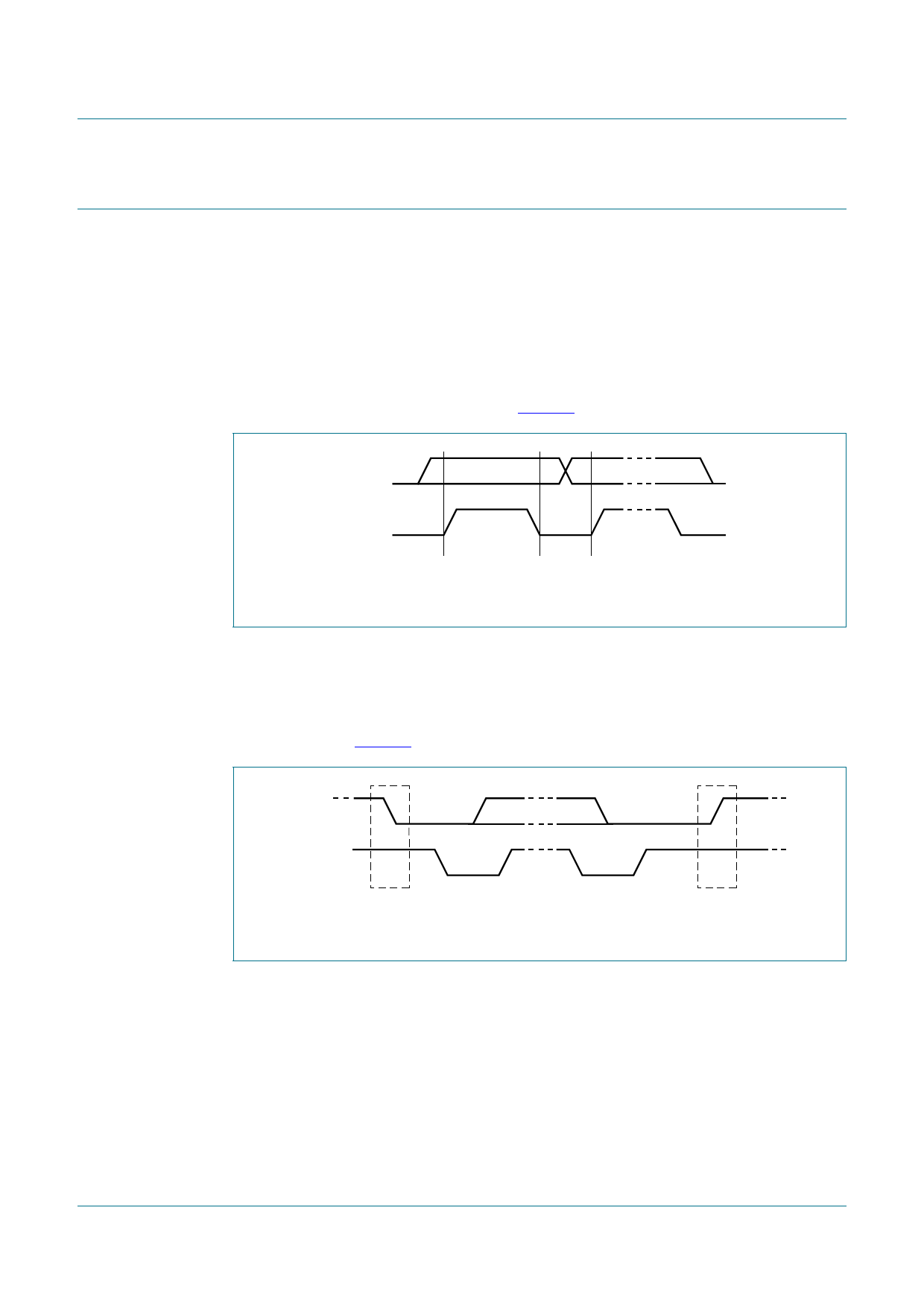

7.1.1 START and STOP conditions

Both data and clock lines remain HIGH when the bus is not busy. A HIGH-to-LOW

transition of the data line while the clock is HIGH is defined as the START condition (S).

A LOW-to-HIGH transition of the data line while the clock is HIGH is defined as the STOP

condition (P) (seeFigure 6.)

SDA

SCL

S

START condition

Fig 6. Definition of START and STOP conditions

P

STOP condition

mba608

PCA9561

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 4 — 6 November 2012

© NXP B.V. 2012. All rights reserved.

9 of 26