MD82C288-10 Ver la hoja de datos (PDF) - Intel

Número de pieza

componentes Descripción

Lista de partido

MD82C288-10 Datasheet PDF : 20 Pages

| |||

M82C288

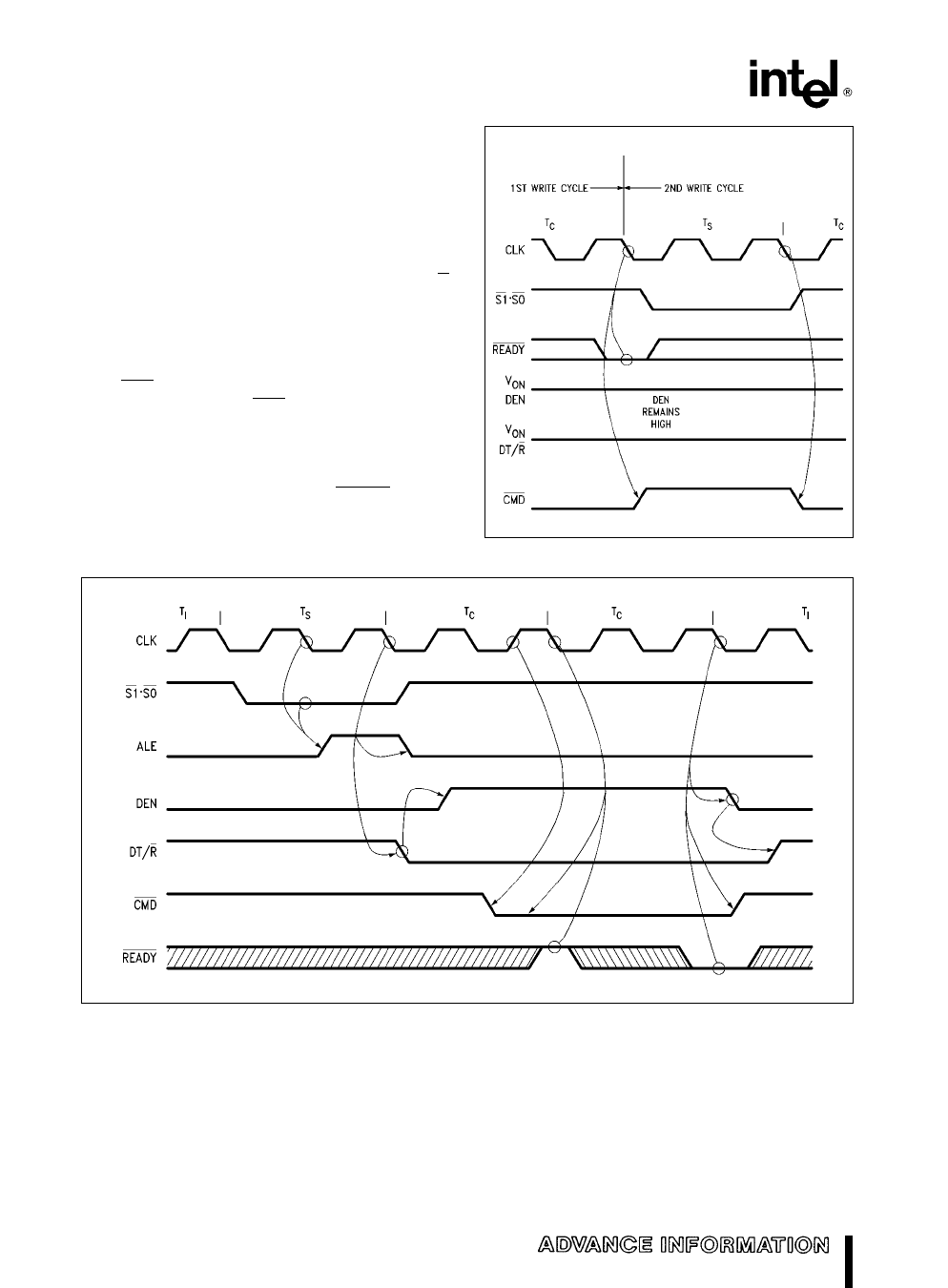

Bus cycles can occur back to back with no TI bus

states between TC and TS Back to back cycles do

not affect the timing of the command and control

outputs Command and control outputs always

reach the states shown for the same clock edge

(within TS TC or following bus state) of a bus cycle

A special case in control timing occurs for back to

back write cycles with MB e 0 In this case DT R

and DEN remain HIGH between the bus cycles (see

Figure 8) The command and ALE output timing

does not change

Figures 9 and 10 show a MULTIBUS I cycle with MB

e 1 AEN and CMDLY are connected to GND The

effects of CMDLY and AEN are described later in

the section on control inputs Figure 9 shows a read

cycle with one wait state and Figure 10 shows a

write cycle with two waits states The second wait

state of the write cycle is shown only for example

purposes and is not required The READY input is

shown to illustate how wait states are added

271077 – 8

Figure 8 Write-Write Bus Cycles with MB e 0

Figure 9 Idle-Read-Idle Bus Cycles with 1 Wait State and with MB e 1

271077 – 9

8