UPD72870 Ver la hoja de datos (PDF) - NEC => Renesas Technology

Número de pieza

componentes Descripción

Lista de partido

UPD72870 Datasheet PDF : 48 Pages

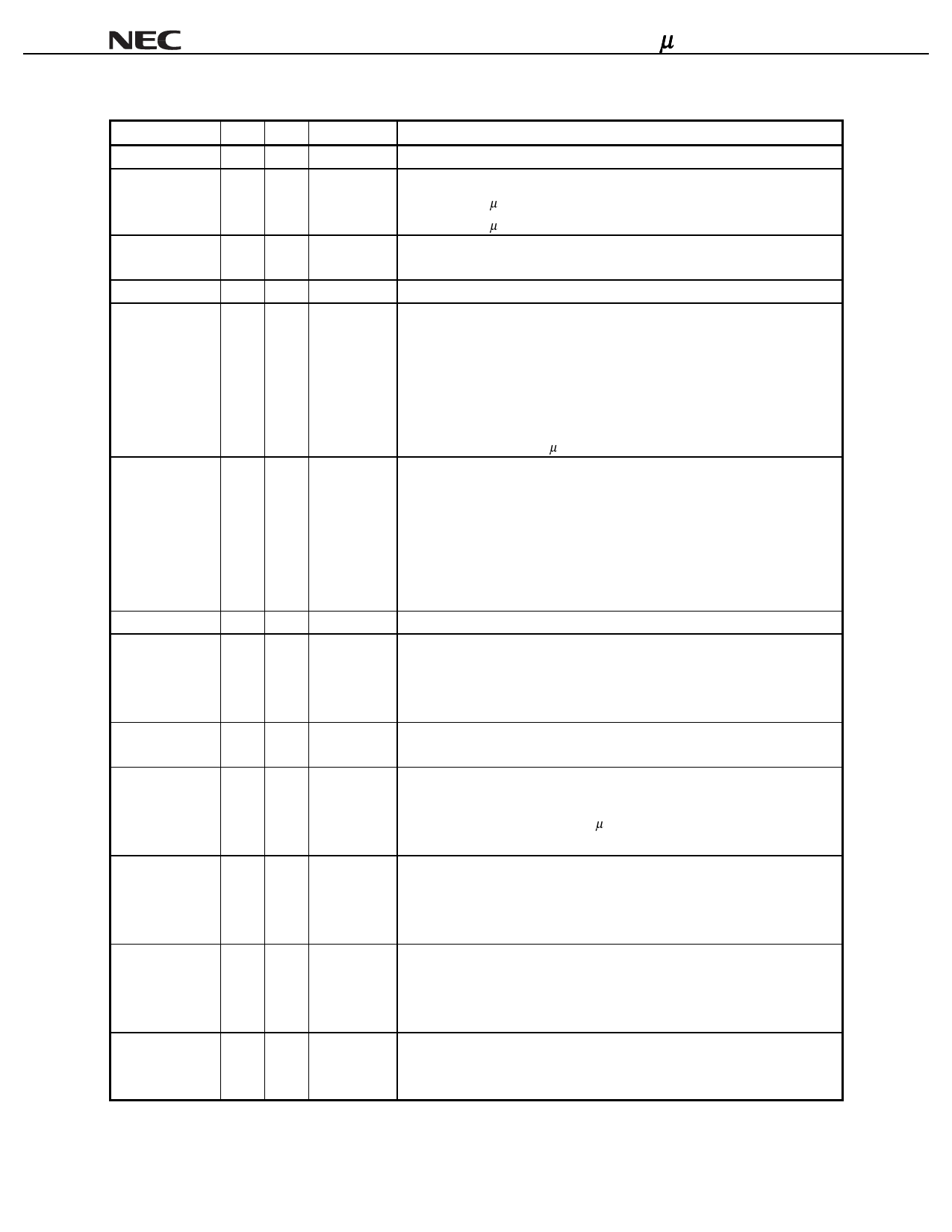

| |||

µPD72870,72871

Field

Extended

Total_ports

Max_speed

Delay

Link_active

5

Contender

Jitter

Pwr_class

Resume_int

ISBR

Loop

Pwr_fail

Timeout

Table 2-1. Bit Field Description (2/3)

Size R/W Reset value

Description

3

R

111

Shows the extended register map.

4

R

0011

or

0001

Supported port number.

0011: 3port (µPD72870)

0001: 1port (µPD72871)

3

R

010

Indicate the maximum speed that this node supports.

010: 98.304, 196.608 and 393.216 Mbps

4

R

0010

Indicate worst case repeating delay time. 144+(2 x 20)=184 nsec

1 R/W

1

Link active.

1: Enable

0: Disable

The logical AND status of this bit and LPS.

State will be referred to “L bit” of Self-ID Packet#0.

The LPS is a PHY/Link interface signal and is defined in P1394a draft 2.0. It

is an internal signal in the µPD72870,72871.

1 R/W

See

Contender.

Description “1” indicate this node support bus manager function. This bit will be referred

to “C bit” of Self-ID Packet#0.

The reset data is depending on CMC pin setting.

CMC pin condition

1: Pull up (Contender)

0: Pull down (Non Contender)

3

R

010

The difference of repeating time (Max.-Min.). (2+1) x 20=60 nsec

3 R/W

See

Power class.

Description Please refer to IEEE1394 -1995 [4.3.4.1].

This bit will be referred to Pwr field of Self-ID Packet#0.

The reset data will be determined by PC0-PC2 Pin status.

1 R/W

0

Resume interrupt enable. When set to 1, if any one port does resume, the

Port_event bit becomes 1.

1 R/W

0

Initiate short (arbitrated) bus reset.

Setting to 1 acquires the bus and begins short bus reset.

Short bus reset signal output : 1.3 µsec

Returns to 0 at the beginning of the bus reset.

1 R/W

0

Loop detection output.

1: Detection

Writing 1 to this bit clears it to 0.

Writing 0 has no effect.

1 R/W

0

Power cable disconnect detect.

It becomes 1 when there is a change from 1 to 0 in the CPS bit.

Writing 1 to this bit clears it to 0.

Writing 0 has no effect.

1 R/W

0

Arbitration state machine time-out.

Writing 1 to this bit clears it to 0.

Writing 0 has no effect.

Preliminary Data Sheet S13925EJ2V0DS00

19