BT869KRF Ver la hoja de datos (PDF) - Conexant Systems

Número de pieza

componentes Descripción

Lista de partido

BT869KRF Datasheet PDF : 104 Pages

| |||

Bt868/Bt869

Flicker-Free Video Encoder with UltrascaleTM Technology

1.0 Functional Description

1.1 Pin Descriptions

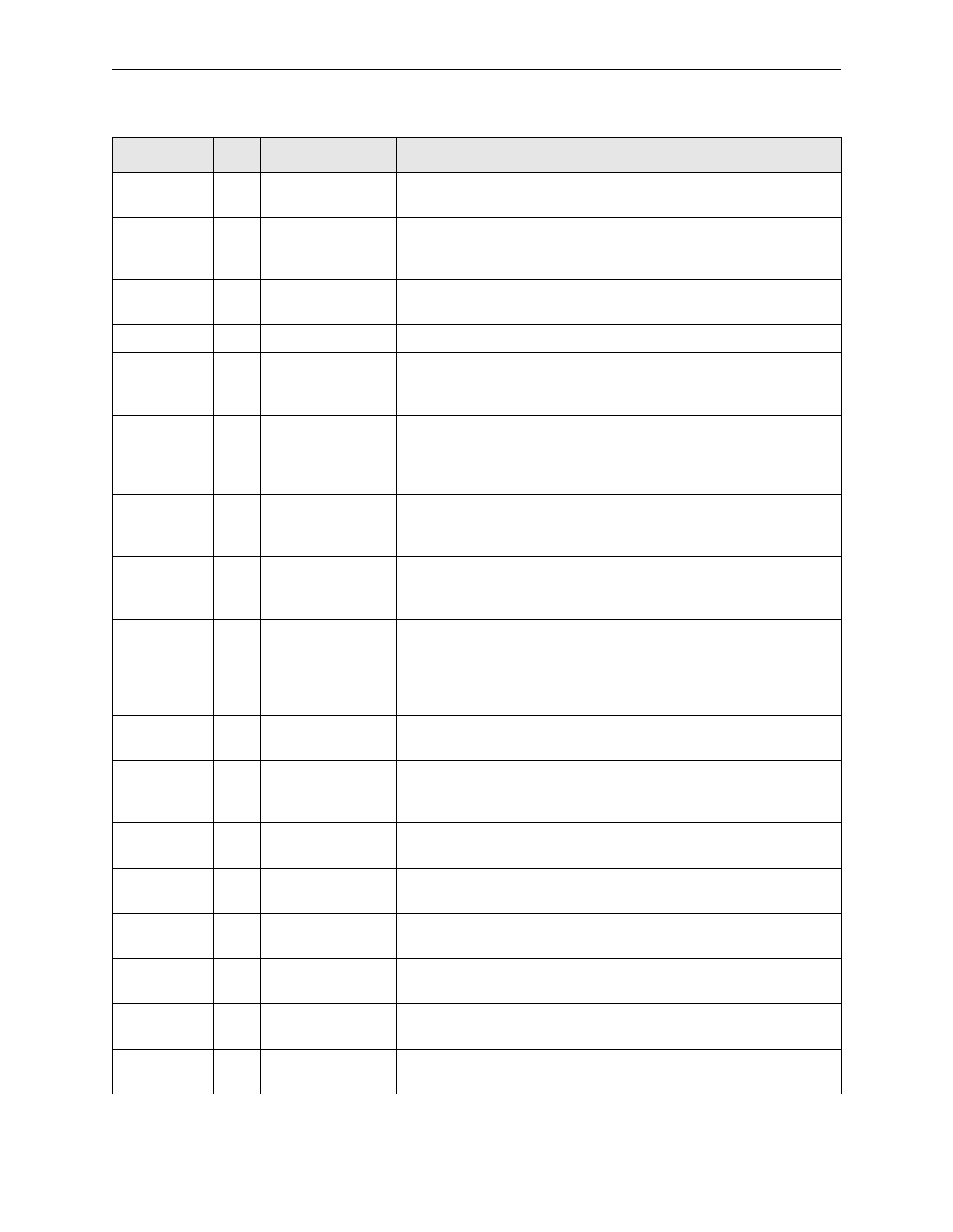

Table 1-1. Pin Assignments (2 of 3)

Pin Name I/O

Pin #

VSS_SI

— 42

VDD_SO

— 46

VSS_SO

TEST

BLANK*

— 43

I 39

I/O 38

FIELD

O 37

VSYNC*

HSYNC*

P[23:0]

I/O 36

I/O 35

I 32–34, 23–29, 5–18

VDD

VDD_I

VDD_O

VSS

VSS_I

VSS_O

VAA

AGND

— 20,40,60

— 19

— 30

— 4, 21, 41

— 22

— 31

— 80

— 1, 79

Description

Serial interface input ground pin. This pin should be tied to the digital

ground plane.

Serial interface output supply pin. This pin should be tied to the proper

supply voltage for the desired serial interface operating voltage (i.e., tie to

5 V for 5 V serial interface compatibility).

Serial interface output ground pin. This pin should be tied to the digital

ground plane.

Test pin. Should be tied to VSS.

Composite blanking control (TTL compatible). This can be generated by the

encoder or supplied from the graphics controller. If internal blanking is used,

this pin can be used to indicate the controller character clock edge.

Field control output (TTL compatible) (Master Mode only three-state in slave

mode). FIELD transitions after the rising edge of CLK, two clock cycles

following falling HSYNC*. It is a logical 0 during odd fields and is a logical 1

during even fields.

Vertical sync input/output (TTL compatible). As an output (master mode

operation), VSYNC* is output following the rising edge of CLK. As an input

(slave mode operation), VSYNC* is registered on the rising edge of CLK.

Horizontal sync input/output (TTL compatible). As an output (master mode

operation), HSYNC* is output following the rising edge of CLK. As an input

(slave mode operation), HSYNC* is registered on the rising edge of CLK.

Pixel inputs. See Table 1-2, “Data Pin Assignments for Multiplexed Modes,”

on page 1.05. The input data is sampled on both the rising and falling edge

of CLK for multiplexed modes, and on the rising edge of clock in

non-multiplexed modes. A higher bit index corresponds to a greater bit

significance.

Digital power for core logic. All VAA and VDD pins must be connected

together on the same PCB plane to prevent latchup.

Digital power for digital inputs. All VAA and VDD pins must be connected

together on the same PCB plane to prevent latchup. This pin should be tied

to the 5 V supply for 5 V tolerant inputs,

Digital power for digital outputs. All VAA and VDD pins must be connected

together on the same PCB plane to prevent latchup.

Digital ground for core logic. All AGND and VSS pins must be connected

together on the same PCB plane to prevent latchup.

Digital ground for inputs. All AGND and VSS pins must be connected

together on the same PCB plane to prevent latchup.

Digital ground for outputs. All AGND and VSS pins must be connected

together on the same PCB plane to prevent latchup.

Analog power. All VAA and VDD pins must be connected together on the

same PCB plane to prevent latchup.

Analog ground. All AGND and VSS pins must be connected together on the

same PCB plane to prevent latchup.

100123B

Conexant

1-3