IC555 Ver la hoja de datos (PDF) - Fairchild Semiconductor

Número de pieza

componentes Descripción

Lista de partido

IC555 Datasheet PDF : 14 Pages

| |||

1. Monostable Operation

Figure 2 illustrates a monostable circuit. In this mode, the timer generates a fixed pulse whenever the trigger voltage

falls below VCC/3. When the trigger pulse voltage applied to the #2 pin falls below VCC/3 while the timer output is low,

the timer's internal flip-flop turns the discharging transistor off and causes the timer output to become high by charging

the external capacitor C1 and setting the flip-flop output at the same time.

The voltage across the external capacitor C1, VC1 increases exponentially with the time constant t = RA*C and

reaches 2 VCC/3 at tD = 1.1 RA*C. Hence, capacitor C1 is charged through resistor RA. The greater the time constant

RAC, the longer it takes for the VC1 to reach 2 VCC/3. In other words, the time constant RAC controls the output pulse

width.

When the applied voltage to the capacitor C1 reaches 2 VCC/3, the comparator on the trigger terminal resets the flip-

flop, turning the discharging transistor on. At this time, C1 begins to discharge and the timer output converts to low.

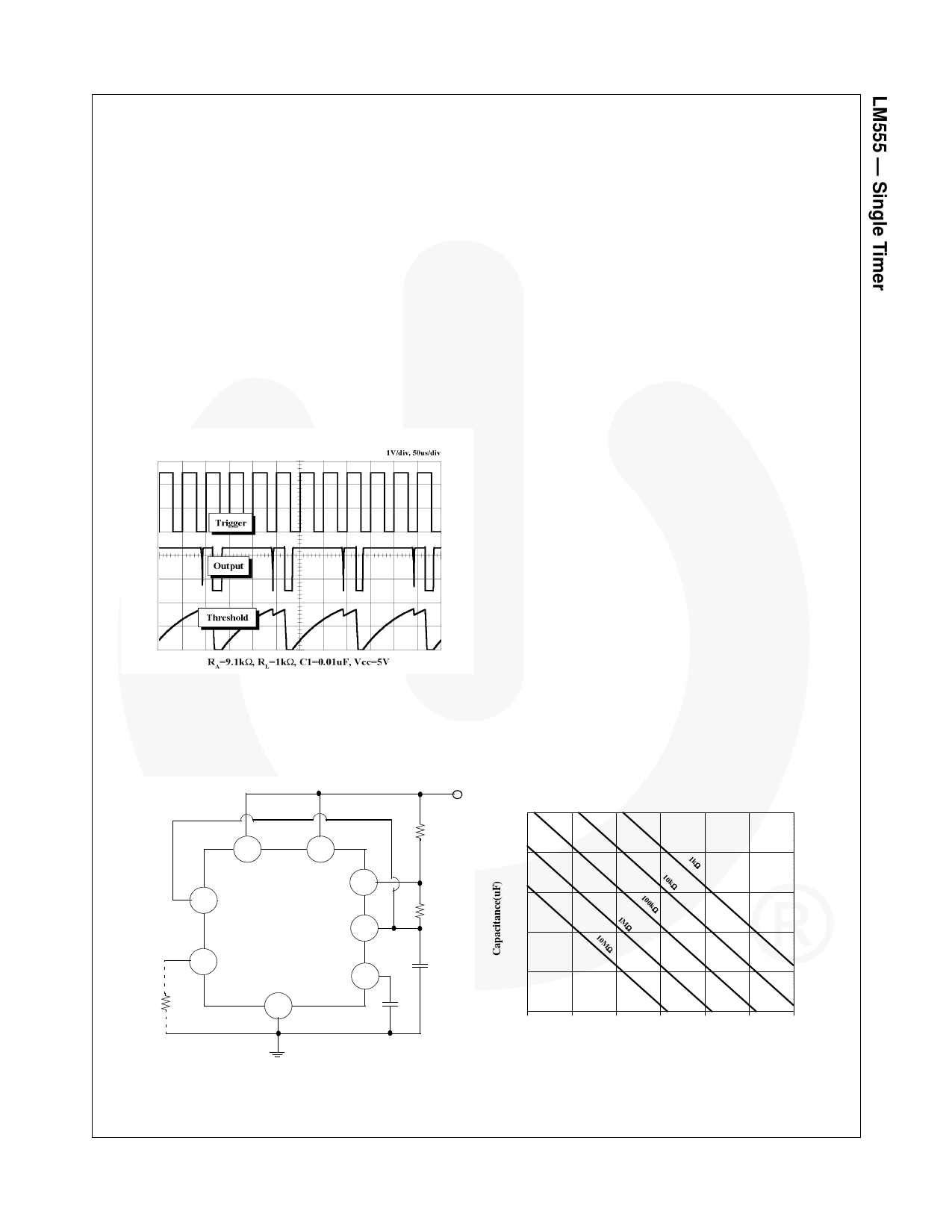

In this way, the timer operating in the monostable repeats the above process. Figure 3 shows the time constant rela-

tionship based on RA and C. Figure 4 shows the general waveforms during the monostable operation.

It must be noted that, for a normal operation, the trigger pulse voltage needs to maintain a minimum of VCC/3 before

the timer output turns low. That is, although the output remains unaffected even if a different trigger pulse is applied

while the output is high, it may be affected and the waveform does not operate properly if the trigger pulse voltage at

the end of the output pulse remains at below VCC/3. Figure 5 shows such a timer output abnormality.

Figure 5. Waveforms of Monostable Operation

(abnormal)

2. Astable Operation

+Vcc

RA

4

8

RESET

Vcc

DISCH 7

2 TRIG

RB

THRES 6

3 OUT

C1

GND CONT 5

RL

1

C2

100

(RA+2RB)

10

1kΩ

10kΩ

1

100kΩ

1MΩ

0.1

10M

Ω

0.01

1E-3

100m

1

10

100

1k

Frequency(Hz)

10k

100k

Figure 6. A Stable Circuit

Figure 7. Capacitance and Resistance vs. Frequency

© 2002 Fairchild Semiconductor Corporation

LM555 Rev. 1.1.0

5

www.fairchildsemi.com