DM9102H Ver la hoja de datos (PDF) - Davicom Semiconductor, Inc.

Número de pieza

componentes Descripción

Lista de partido

DM9102H Datasheet PDF : 77 Pages

| |||

DM9102H

Single Chip Fast Ethernet NIC Controller

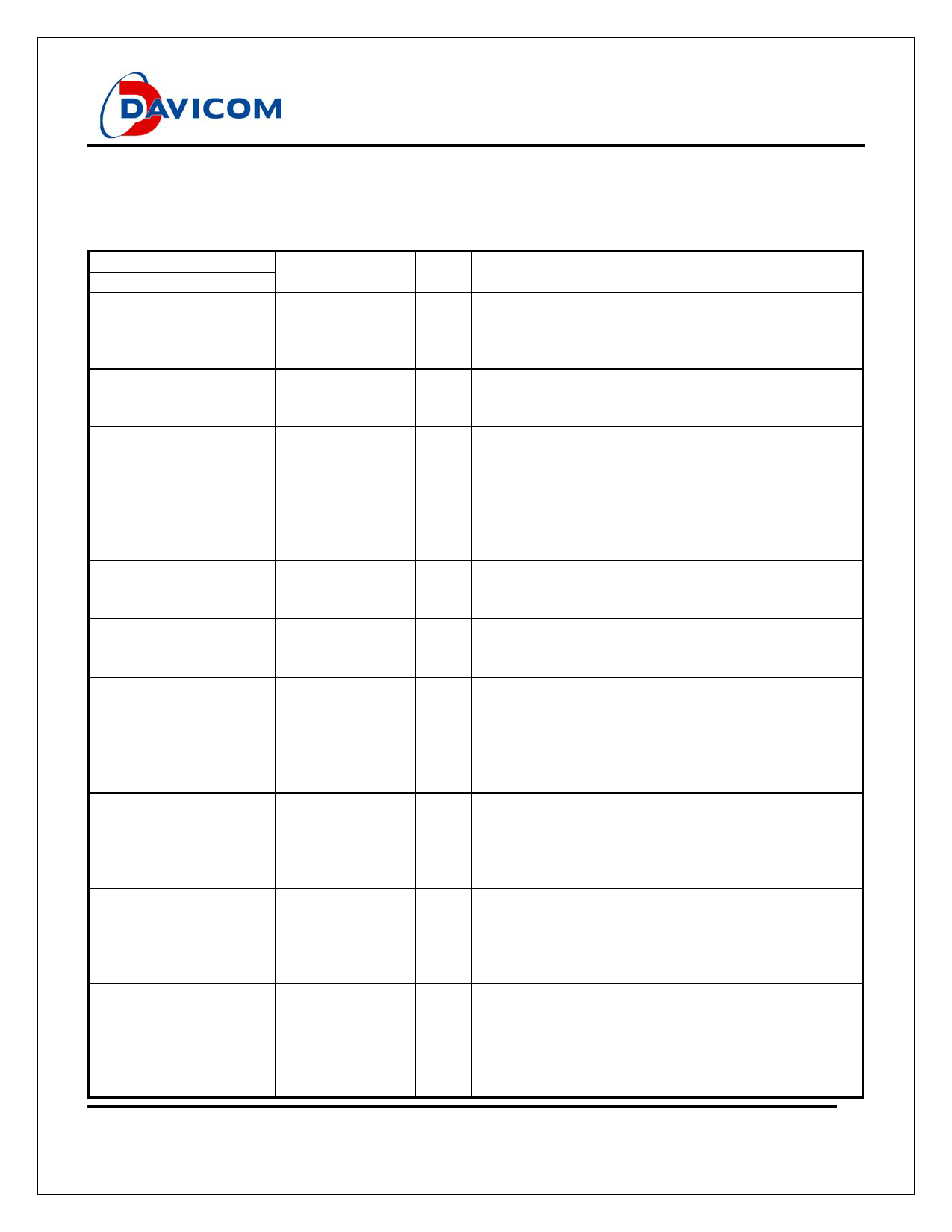

5. Pin Description

I = Input, O = Output, I/O = Input / Output, O/D = Open Drain, P = Power,

LI = reset Latch Input, # = asserted Low

5.1 PCI Bus Interface Signals

Pin No.

Pin Name

I/O

Description

128LQFP

113

INT#

O/D Interrupt Request

This signal will be asserted low when an interrupted condition

as defined in CR5 is set, and the corresponding mask bit in

CR7 is cleared.

114

RST#

I System Reset

When this signal is low, the DM9102H performs the internal

system reset to its initial state.

115

PCICLK

I PCI system clock

PCI bus clock that provides timing for DM9102H related to

PCI bus transactions. The clock frequency range is up to

40MHz.

117

GNT#

I Bus Grant

This signal is asserted low to indicate that DM9102H has

been granted ownership of the bus by the central arbiter.

118

REQ#

O Bus Request

The DM9102H will assert this signal low to request the

ownership of the bus.

119

PME#

O/D Power Management Event.

Open drain. Active Low. The DM9102H drives it low to

indicate that a power management event has occurred.

3

IDSEL

I Initialization Device Select

This signal is asserted high during the Configuration Space

read/write access.

21

FRAME#

I/O Cycle Frame

This signal is driven low by the DM9102H master mode to

indicate the beginning and duration of a bus transaction.

23

IRDY#

I/O Initiator Ready

This signal is driven low when the master is ready to

complete the current data phase of the transaction. A data

phase is completed on any clock when both IRDY# and

TRDY# are sampled asserted.

24

TRDY#

I/O Target Ready

This signal is driven low when the target is ready to complete

the current data phase of the transaction. During a read, it

indicates that valid data is asserted. During a write, it

indicates that the target is prepared to accept data.

26

DEVSEL#

I/O Device Select

The DM9102H asserts the signal low when it recognizes its

target address after FRAME# is asserted. As a bus master,

the DM9102H will sample this signal which insures its

destination address of the data transfer is recognized by a

target.

Final

3

Version: DM9102H-12-DS-F01

February 15, 2008